导言

笔者2008年在本刊宣布过一篇文章《MCU需求改善》,本文就为什么要改,怎么改作进一步的评论。总的来说,由于对功用安全要求的知道深化,改善的必要则突现;并且国际上现已有了满意改善的产品,改善事实上已开端,不做的人失掉的是竞争力,改善其实也不杂乱。

1 发生错的原因与现有对策

MCU在作业时会遭到搅扰,在一些空间场合,或许遇到粒子炮击而发生稳态的翻转,即所谓single event upset。而一般工业场合是电源传导搅扰,受搅扰时,电源电压会瞬间超出或许稍微超出MCU的名义作业电压,线路的稳定性就无法确保。由于各单个逻辑电路工艺进程中总会有细小差异,电源电压的稍微超出会在最弱的逻辑电路中形成指令读过错和数据读写过错。这种过错终究表现为数据的过错。

国外对DRAM犯错的研讨已做得许多,在参阅文献中转述了犯错的概率:“谷歌(Google)运用了很多服务器,2009年的大规模核算。犯错的概率是2.5~7×10-11error/bit/h。”即8G RAM每小时会有5个错。

现在关于有功用安全要求的体系,安全等级为SIL2时,犯错的概率应小于10-7”/h。现在操控器所用的MCU的Flash与RAM的巨细已达128 K~1 Mb,参阅上述概率,假如短少程序的维护,将会有1M×7×10-11 error/h=7×10-5 error/h,这远大于功用安全要求的犯错概率。

从功用安全的视点,体系中任何影响功用的过错都是应该被检测出来的,假如这个过错危及人类生命或形成设备的重大损失,那么就必须有防备的办法,必要时就必须纠正过错。然而要到达这种要求是很难的,需求支付很大的价值。以数据过错为例,人们常常重复核算屡次,然后把占多数的成果代表正确的成果。这样,数据共享前的成果都要经表决,不然发现错会太晚,影响一致性。这就需求更多的硬件资源与开发本钱。即便如此,假如作为表决器的环节仍是MCU的一个程序,它依然或许会受过错指令的搅扰,未能彻底拦住过错。

为了节约本钱,更多的运用并没有选用这种冗余与表决的办法。它们往往以不死机作为方针,只需不死机,由操控目标来的新信息就能够重算出新的正确成果。即便上一次算出的错了,其成果也只连续了一个采样周期。这种战略对有累积效应的运用是无效的,就像参阅文献中评论的积分功用会失利。又如运转成果与进程密切相关的运用,例如可编程操控器(PLC),数据的过错会导致操控逻辑的紊乱。

确保不死机的首要办法是选用看门狗技能,假如程序走飞,在必定时间内没有复位计时器,计时器就会溢出,发生MCU的从头启动,从头初始化能够纠正损坏了的数据。看门狗技能是不论数据正确性的,由于指令错了程序未必走飞,而指令错了数据错的或许性极大。

2 过错现象与过错校对计划

MCU的指令在读取时发生过错就会发生不同的履行成果,在参阅文献中以8051的MOV指令为例,当有一位读错时就变成跳转、除法、减法、交流、增1等等指令。实际上大部分MCU都会有指令错而履行成果错的问题,由于这些指令内没有查验错的机制。MC68HC11的LDA指令有1位错时或许转为加法、减法、送当即数到累加器B、送状况存器、送仓库指针等指令,如表1所列。

尽管笔者注意到这种犯错的或许性比较早(1990年),可是在写参阅文献时(2008年)并不知道Freescale公司(2005年)的16位单片机中现已有了对指令增加检错与纠错的办法。参阅文献中说到:“当体系遇到强搅扰时,CPU在读取指令或数据时或许呈现过错,假如指令或数据只是是某一位呈现过错,ECC模块会主动纠正这一位的过错,使体系照旧运转,假如呈现二位或二位以上的过错,则ECC会以中止办法告诉CPU,呈现了读程序错或读数据错。”

依据参阅文献,Freescale公司的16位单片机MC9S12P128的Flash部分32位的程序有7位特征,构成纠错编码(error correction code),能够纠正1位错和发现2位错。Flash部分16位的数据有6位特征,构成纠错编码ECC,能够纠正1位错和发现2位错。因而对指令的检错纠错现已是批量运用了。最近AMD也推出了G系列嵌入式SoC渠道,它也选用了ECC技能。

ECC技能在企业级服务器中运用比较早,它考虑了DRAM的特色,例如内存插条中由多个芯片构成,就从每个芯片的对应位集合起来,再加校验位。然后又有对应的确诊规划,能够找出犯错多的内存条,以便替换。所以它与单片机上的运用情况仍是有差异的(替换是不或许的),直接照抄是不用要的。

从Freescale公司的ECC可知,它的海明间隔HD=3,并且选用了纠错办法。假如只是检错,那么完成起来更简略一点。检测犯错后的处理办法就比较简单规划,例如发生中止,把该指令重取,由所以硬件中的办法,不用考虑增参加栈/出栈维护现场的动作,开支很少。假如必要,还能够在别的的当地保存犯错核算信息,以及触发更杂乱的维护办法。

3 简化报错与纠错计划

从现在单片机的发展趋势来看,由于32位单片机价格的下降,商场将分化为8位与32位南北极。在我国8位机首要是8051体系,现已培养了较大的商场和很多了解的人才,并且也有克己8051的才能,所以在8051上增加查验码是合理的挑选。假如增加了这一功用,无疑会进步运用8051体系的可信赖性,提高产品层次,延伸产品的寿数周期。另一方面,其完成也比较简略,信任根据ARM的32位机也会增加这种指令查验机制,本钱也要上升。

对MCU程序加维护的厂家还不多见,即便是Freescale公司也还没有对一切的MCU增加维护,由于增加维护是要增加本钱的,所以增加维护的办法是值得研讨的课题。

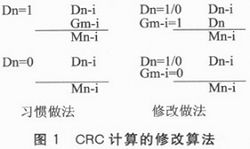

关于8位指令代码检错,能够挑选低阶次的CRC。由参阅文献可知能够选4位CRC,其生成多项式是G=X4+X+1。它能够确保HD=3的数据字长为11位,已超越所需的8位。这儿由于数据字8位是一次取出,所以CRC是并行核算的,由数据字到CRC的求取的办法推导如图1所示。

假定数据字用D表明,生成多项式用G表明,Gm为最高阶的系数,等于1。那么习气的做法在除到Dn位时,判别Dn值。若Dn=1,则将G和D的对应位对齐,用模2加法求取余数,Mn-i=Dn-i+Gm-i,用余数Mn-i替代本来的Dn-i移位。假如Dn=0,则不做加法,Mn-i=Dn-i,然后移位,也能够说用余数Mn-i替代本来的Dn-i移位。咱们的意图是直接由D来发生余数,所以做了修正。修正办法是,当对齐后的Gm- i=1时,取Mn-i=Dn-i+Dn。当Gm-i=0时,对应项不做模2加。现在证明这两种办法是等效的:

Dn=0,Gm-i=0时,习气办法Mn-i=Dn-i;修正办法Mn-i=Dn-i。

Dn=0,Gm-i=1时,习气办法Mn-i=Dn-i;修正办法Mn-i=Dn-i+Dn=Dn-i。

Dn=1,Gm-i=0时,习气办法Mn-i=Dn-i+Gm-i=Dn-i;修正办法Mn-i=Dn-i。

Dn=1,Gm-i=1时,习气办法Mn-i=Dn-i+Gm-i=Dn-i+1;修正办法Mn-i=Dn-i+Dn=Dn-i+1。

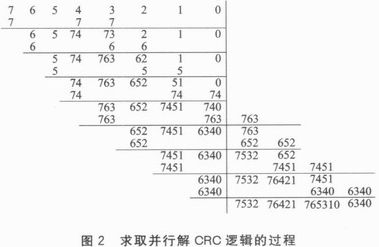

现在对G=X4+X+1时8位指令的数据字用修正办法求取CRC各位的值,为了阅览便利,将数据字的各位用数字代表,例如7代表D7。参加模2加的各位就以各数字连写在一起。例如CRC的最高一位是7 532,它代表D7、D5、D3、D2的模2加法成果。经过树立真值表,它们最终都能够用组合逻辑来完成,所以在取指完成后就当即能够判出是否有错。求取并行解CRC逻辑的进程如图2所示。

这种推导并行CRC值的办法也能够用于较长的指令,当然,为了防止手算的过错,应该以程序来求,这不是难事。

8位指令用4位CRC维护开支是大了一点,可是它的维护强度也大了,关于16位的指令程序,用二次8位维护,有4个错是必定能够检测出来的,假如像Freescale技能用掉6位维护,只能确保有2个错能够检测出来。所以这是折中的办法。

关于16位指令,能够用5位CRC维护,参阅文献中G=X5+X2+1能够在26位数据字长上取得HD=3。关于32位指令,能够用6位CRC维护,参阅文献中G=X6+X+1能够在57位数据字长上取得HD=3。由此可见,假如仅检错而靠重传作纠错,校验项比Freescale都要省一位,用重取指令的办法能够节约开支。

这种办法也能够对数据存取加以维护。在以现有MCU为主的单板嵌入式核算机中,增加程序维护也有很重要的含义,怎么施行是值得研讨的课题。