I2C总线,是INTER-IC串行总线的缩写。INTER-IC原文粗心是用于相互作用的集成电路,这种集成电路首要由双向串行时钟线SCL和双向串行数据线SDA两条线路组成,由荷兰菲利浦公司于80年代研制开发成功。

I2C总线在传送数据时其速率可达100kbps,最高速率时可达400kbps,总线上答应衔接的设备数首要决议于总线上的电容量,一般设定为400pF以下。I2C总线首要在微处理器的操控之下,因而一般称微处理器是I2C总线的主机。习惯上总称受控设备及功用电路为I2C总线的从机。这种主机与从机之间的衔接一般是在总线的输出端,而输出端的电路结构为I2C总线的从机。这种主机与从机之间的衔接一般是在总线的输出端,而输出端的电路结构又总是开漏输出或集电极开路输出。 一般数据传送要由主机宣布发动信号和时钟信号,向所控从机宣布一个地址、一个读写位和一个应对位,其间地址位为7位数据,在实践操控中,一般一次只能传送一个8位数据,并以一个中止位完毕。

在实践使用中,往往被传送的数据位数会超越8位,也便是说总会有多字节传送,这时有必要在传送数据地址完毕后再传送一个副地址。因而,被传送的字节没有约束,但每一个字节后边有必要有一位应对位。应对位一般被设定在低电平,当应对位处于高电平时,指示被传送的数据已完毕。

I2C总线在闲暇状况时,也便是不在进行任何操作操控时,数据线SDA和时钟线SCL总是处于高电平输出状况。当操作操控系统时,I2C总线的主机将宣布发动信号,使数据线SDA由高电平变为低电平,一起时钟线SCL也宣布时钟信号。

I2C总线在传送数据时,总是将最高位数堆放在前面作为其特有的传送次第。在数据传送进程中,假如从机在完结某一操作之前不能接纳下一个字节数据,即数据中止,这时时钟线SCL将被位至低电平,然后迫使发送器主机进入等候状况,当接纳器从机准备好接纳下一个字节时再开释时钟线SCL,持续传送数据。

在I2C总线的操控系统中,有时从机也可所以多台微处理器,在多台微机一起作业时,它们对总线的操控也由类似于时钟的同步方法进行裁定,也便是说时钟的同步与裁定进程是一起进行的,不存在因是主机而有优先权次第。不同速度的从机能够接在同一I2C总线上完结相互间数据的传送。高速方法芯片和一般芯片能够混合于同一I2C总线上。

I2C总线的特色与特性

I2C总线与传统的PWM调宽脉冲相比较,其最大的特色是串行数据线和时钟线都是双向传输线。I2C总线在实践电路的使用中,两根线各自经过一个上拉电阻衔接到电源电压的正极点,当总线闲暇时,数据线SDA和时钟线SCL有必要坚持高电平,一起各接口电路的输出又有必要是开路漏极或开路集电极,因而I2C总线的最大特性是在地址信息传输进程中,即可所以主控器也可所以被控器,或既可所以发射器又可所以接纳器,然后为挂在总线上的各集成电路或功用模块完结各自的功用供给了极大便利。

假如I2C总线用作主控器电路即微处理电路,则在总线大将供给时钟传送及初始化的数据传输,而操控数据信息传送的目标、方向及传送的中止也由主控器来决议。在I2C总线上被主控器所寻址的集成电路或功用模块,称之为被控器。在I2C总线上,被控器每接纳一个“数码”后都要在数据线上给主控器发送一个辨认应对信号,以示完结一个操控功用。因而,I2C总线具有非常灵敏的运用性。而且还具有多重主控的才能,如多个作为主控器去操控占用总线的电路,都能够依据在I2C总线进步行数据传送的作业状况,被分为主控发送器、主控接纳器、被控发射器、被控接纳器。在多重主控才能中,因为总线的裁定进程,I2C总线的时钟信号将是各试力占用总线的各主控器的时钟信号的同步组合。所谓裁定是在多个主控器妄图一起操控总线时一个判定进程,它只答应其间的一个主控器持续占用总线,并确保在整个进程中总线上的数据不会被丢掉或出过错;所谓同步是将两个或多个器材的时钟信号进行处理。

I2C总线上的时钟信号是由主控器发生,每个主控器在占用总线传送数据期间都有自已的时钟,因而,在使用中,由一个主控器发生的I2C总线时钟信号只或许被一个低速的被控器或另一个主控器改动。可是,一个低速的被控器可将串行时钟线坚持低电平,以延伸总线时钟信号的低电平周期,使高速的主控器和低速的被控器到达同步,因而,当总线上正在进行裁定时,另一个主控器也能改动总线的时钟周期。

I2C总线的操控技能

因为在I2C总线中的多主控器的操控权总是相互竞争,而且在相互竞争中进行寻址和数据发送,因而总线上没有中心微处理器,也没有任何优先级。在I2C总线进步行数据传输时,一切的主控器都会在串行时钟线上发生自己的时钟信号,而且只要当时钟线上的信号处于高电平时,数据线上的数据才是有用的。因而,当各主控器向总线上输出各不相同的时钟频率时,只要经过裁定进程,才可使总线上有一个共同的时钟信号。只要总线上的时钟线上的一种“线与”衔接和双向传输特性来完结的。因而,I2C总线的操控根底首要是裁定进程和时钟同步。

在总线的裁定进程中,一旦有一主控器输出一个低电平时钟信号,则串行时钟线将由此变为低电平,直到该主控器时钟信号的高电平状况到来,数据信号才开端传送。在总线上这个时钟线的电平转化,将影响一切主控器的时钟信号低电平周期的计时。事实上,当一个主控器的时钟信号由低电平向高电平转化时,它或许并不会改动串行时钟线的低电平状况,因为此刻或许有另一个主控器依然处于时钟低电平周期。也便是说,在I2C总线操控中,时钟线将由时钟低电平周期最长的首要控器坚持为低电平状况,而其他时钟低电平周期较短的主控器则将相继进入时钟高电平等候状况。只要当总线上的一切主控器都完毕了时钟低电平周期的计时后,时钟线才被彻底开释,即时钟线的状况到达共同高电平状况。

当一切主控器时钟信号都进入高电平状况后,便开端了各自的时钟信号高电平周期计时。当有一个主控器的时钟高电平状况计时完毕时,这个主控器将再次使I2C总线上的时钟线SCL处于低电平状况。然后,在总线的裁定进程中,使时钟线经过各主控的时钟输出发生一个共同的时钟同步信号成为实践。

简言之,在多重主控器的I2C总线上,时钟线信号的低电平周期由时钟信号低电平周期最长的主控器决议,而时钟线信号的高电平周期则由时钟信号高电平周期最短的主控器决议。

在I2C总线中,具有主控才能的器材的数据传输和寻址也是在裁定中进行的。当有多个主控器妄图一起占用总线传输数据时,依据I2C总线的规约它们之间会有一个促裁进程,以决议谁将占用总线。促裁是在时钟线SCL为高电平时,依据数据线SDA的状况进行的。因而,裁定进程和时钟电平、数据线状况是相得益彰的。也正是这种相得益彰的机制,使在总线裁定进程中,当有其他主控器在数据线上传送低电平时,发送高电平的主控器将会发现此刻数据线上的电平与其输出电平不共同,然后被判定失掉总线的主控权,并当即封闭其数据输出。裁定进程能够持续诈多位,以对多个主控器正在妄图寻址同一电路的事情进行判定。假如一个主控器在发送某一字节期间被判定失掉主控权,则它的时钟信号可持续输出,直到整个字节发送完毕中止。假如主控器在其寻址阶段被裁定决议失掉主控权,则该主控器有必要马上进入被控接纳器状况,以判定被裁定决议取得主控权的主控器是否正在对它进行寻址。发生数据的主控器一旦发现内部数据电平与数据总线的实践电平之间有差异,则它的输出将被当即封闭,随即在总线上输出一个高电平(开释总线),这就不会影响取得主控权的主控器所进行的数据传输,总线上的寻址和数据传输等住处也不会丢掉。因而,I2C总线的裁定进程使I2C总线上的数据传输得以顺利进行,为多种操控功用的施行奠定了杰出的根底。

I2C总线的传输

I2C总线的传输是一个比较复杂的数码传输,它首要是以8bit的字节进行数据传输,而传输时又总有一个时钟脉冲相对应,因而,I2C总线的数据传送实质上是个脉冲串的传输,其传输格局如图1-14所示。图中1为字节传送完结接纳器内发生中止信号,2为当处理中止服务时时钟线坚持低电平。

在I2C总线上,每一个数据中,逻辑“0”和逻辑“1”的信号电平取决于相应的正端电压。I2C总线在进行传送时,在时钟信号为高电平期间,数据线上的数据有必要坚持安稳,只要在时钟线上的信号为低电平期间,数据线上的高电平或低电平状况才答应改动。这就坚持了数据传输的有用性。

在时钟线坚持高电平期间,因为数据线由高电平向低电平的改动是一种安稳的状况,所以就将其状况规定为开端条件;而当时钟线坚持高电平期间,数据线是由低电平向高电平改动,则规定为中止条件。只要I2C总线中主控器发生开端条件和中止条件两个信号时,总线才会被以为处于“忙”态或“闲”态,然后精确操控了比特位的传送。

在I2C总线上,比特位传送字节的后边都有必要跟从一位承认位,或称跟从一位应对位。而且数据是以最高有用位首要宣布。可是,当正在进行数据传输的接纳器收到完好的一个数据字节后,有或许还要完结一些其他的工和,如处理一个内部中止服务等。在这种情况下就有或许无法马上接纳另一字节的数据,因而,此刻接纳器能够经过总线上的时钟坚持为低电平,然后使发送器进入等候状况,直到接纳器准备好接纳新的数据,而接纳器经过开释时钟线使数据传输持续进行,正是I2C总线能答应其他总线的数据格局进行传输,才有一个特别寻址开端的信息传输,以及经过对总线发生一个中止信号进行中止。

当一个字节的数据能够被总线上的一个已被寻址的接纳器接纳后,总线上的一般要发生一个承认信号,并在这一位时钟信号的整个高电平期间,使数据坚持安稳的低电平状况,然后完结应对承认信号的输出。承认信号一般是指开端信号和中止信号,假如这个信息是一个开端字节,或是总线寻址,则总线上不答应有应对信号发生。假如因某种特别情况,被控器不对应的被控寻址进行承认答复,则有必要将数据线置于高电平,然后主控器能够经过产一个中止信号来完毕总线的数据传输。假如被控接纳器对被控寻址做出了承认应对,但在数据传输的一段时间今后,又无法持续接纳更多的数据,则主控器也将中止数据的持续传送。因而,被控接纳器能够经过对无法接纳的榜首个数据字节不发生承认应对信号来告诉主控器,即在相应的应对信号时钟位大将数据线置于高电平,主控器则在总线上发生中止信号,然后完毕数据的传送。

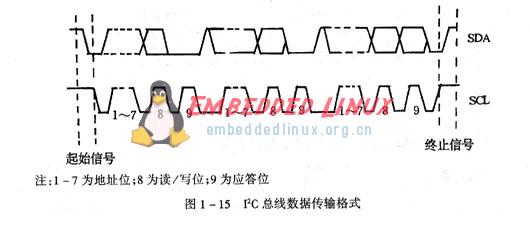

注:1-7 为地址位;8为读/写位;9为应对位

在I2C总线上,它的数据传输总有一些规约要求,例如,开端信号的后边总有一个被控器的地址。被控器的地址一般规定为7bit的数据,数码中的第8比特是数据的传输方向位,即读/写位。一个完好的I2C总线传输格局如图1-15所示。

在读/写位中,假如是“0”,则表明主控器发送数据,也便是履行“写”的功用;假如是“1”,则表明主控器接纳数据,也便是履行“读”的功用。而数据的每次传输总是随主控器发生的中止信号而完毕。而I2C总线中,有时主控器期望总占用总线,并不断进行数据传输,因而,在设定规约时,能够在不首要发生信号的情况下,再次宣布开端信号对另一被控器进行寻址。为处理这一问题,能够选用多种读/写组合方式来进行总线的一次数据传输。在多种读/写组合方式中,首要有三种办法,其间:

1.主控发送器向被接纳器发送数据,数据传输方向在整个传输进程中不变。

2.主控器在榜首个字节后当即从被操控器读数据,在首位承认应对信号发生后,主控发送器变成主控接纳器,而被接纳器变成被控发送器,一起首位应对信号仍由被控器发生,使中止信号总是由主控器发生。

3.数据传输进程中的复合格局需求改动传送方向时,开端信号和被控器地址都会被重复发生一次,但两次的读/写方向正好反相。

总之在I2C总线上,经过接口电路收到开端信号后,有必要复位它们的总线逻辑,以使被操控器地址的传输得以预处理,然后完结对各不相同功用电路的操控