摘要:

跟着科学技术一日千里,核算机使用的遍及,带来了软件开发范畴的蓬勃开展,软件开发的艰苦与软件盗用的垂手可得,让许多不法盗版商享用到了人间难有的免费午饭,而软件开发者和版权所有者看着自己艰苦奋斗得到的劳动成果却只能感叹万分。所以,怎么维护开发软件的版权,变得越来越重要了,咱们不行能把版权的维护只是寄托在有关的法律上,并且施行版权的自我维护也成为必要的手法。

跟着嵌入式体系逐步走进咱们的日常日子,它也渐渐地和Windows相同为人熟知,作为使用软件,嵌入式软件虽然面临的不是终究的顾客,而是硬件出产厂商,虽然不会容易发生盗版软件的现象,但怎么量化软件的使用量,怎么维护软件厂商的利益,这也是咱们作为软件开发者和版权所有者值得注重的问题。

本项目规划计划是根据FPGA的嵌入式安全保密模块ESMF (Embedded Security Module based on FPGA),并经过高密核算回来安全认证码,经过安全认证码与密匙校验,为用户处理高密数据存储、身份认证等许多安全问题,这将为软件版权的维护供给有用的途径。

1、项目布景

1.1 研讨布景

现在核算机使用的飞速开展,使得软件的使用也日新月异,促进了软件开发范畴高速的开展,使得人们的学习、作业、日子更为快捷、简略、高效!可当咱们感触软件给咱们带来利益的一起,又有谁会去怜惜那些勤劳为软件开发做出献身的开发者和版权所者的劳动成果呢?因而,软件开发者和版权所者就怎么处理维护软件的版权问题,就显得尤为急切。

本规划项目经过ESMF规划,有用地处理了维护软件版权的问题,完结一套软件对应一个密匙的形式,然后到达对软件版权施行强有力的维护。

1.2 本项意图长处

本项目选用硬件描绘言语Verilog HDL进行编程规划,首要完结根据FPGA的嵌入式安全保密模块ESMF的规划,经过安全保密保密模块ESMF成功的身份认证,使用软件才会持续运转,不然,软件停止履行,然后起到软件版权的维护效果。

本规划项目具有如下长处:

(1)具有高性价比、高安全性、高可靠性。

(2)嵌入式安全保密模块ESMF具有仅有的序列号S/N。

(3)电路规划简略,易编程,高效率。

1.3使用拓宽

本规划项目可使用其他保密范畴,比如稳妥柜职业,稳妥密匙,安全稳妥门等。

2、项目计划

2.1 完结功用

选用硬件描绘言语Verilog HDL进行规划,内部完结Chaos加密算法,过串行接口与外部芯片进行数据交换。终究封装为IP核,方便在FPGA器材中调用与完结。具有高性价比、高安全性、高可靠性的特色,使用于各种嵌入式终端完结数据的安全存储,完结终端的身份辨认与认证等功用。

2.2 计划规划原理

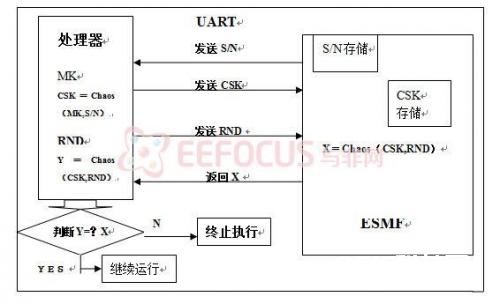

本项目是根据FPGA的嵌入式安全保密模块ESMF,完结软件运转前需求身份认证,以下为本规划项目施行计划的硬件体系结构图:

图1 根据FPGA的嵌入式安全保密模块ESMF

2.3 认证流程

外接处理器首要分为数据发送、数据接纳和数据处理部分。

身份认证进程如下:

- ESMF复位,从S/N存储器中调出序列号S/N,向处理器发送序列号S/N。

- 处理器提取预设的编码MK,经过Chaos加密算法CSK=Chaos(MK,S/N),核算得出密钥CSK。

- 处理器发送CSK,把CSK保存到CSK存储器中。

- 处理器随机发生一个随机数RND,经过Chaos加密算法Y=Chaos(CSK,RND),核算得出Y值。

- 处理器把随机数RND发送给ESMF。

- ESMF接纳到RND后,调用密钥SCK,经过Chaos加密算法X=Chaos(CSK,RND),核算得出X值。

- 将X值回来到处理器,将X与Y进行校验,判别是否持平。若X与Y持平,那么身份认证成功,软件持续运转,不然,软件停止履行。

以下是体系运转的流程图:

图2 身份认证流程图