跟着核算机、DSP、超大规模集成电路等技能的开展,画面切割器开端选用硬件规划。首要,将各路视频信号转换成数字视频信号;然后,在数字范畴对各路视频信号进行处理。使电路的规划、调试得到了很大的改进。可是,规划中所运用的独立的逻辑电路较多,有的乃至运用专用的DSP芯片去处理视频画面的切割。虽然能够满意对视频图画数据处理速度的要求,可是还需求外加CPU去协调体系作业,使得整个体系仍显得体积较大,并且体系本钱较高。跟着半导体加工工艺的不断开展,FPGA在结构、速度、工艺、集成度和功用方面都取得了很大的前进和进步。本文将具体介绍依据FPGA开发技能的视频图画画面切割器的软硬件规划与完结。

1 体系总体规划

本体系选用ALTEra公司的CycloneIII系列中的EP3C40F780C7类型FPGA作为中心处理芯片,提出和规划了一个多路视频图画数据的收集、处理、显现,完结视频图画画面切割器。

Cyclone III系列FPGA是Altera公司的低功耗、高功用和低本钱的可编程逻辑器材,具有共同的低功耗体系结构,以十分低的本钱供给丰厚的存储器和专用乘法器资源。在视频和图画处理等高强度算法使用中,这些特性使该FPGA成为ASSP、ASIC以及分立数字信号处理器的抱负代替计划。

1.1 硬件结构规划

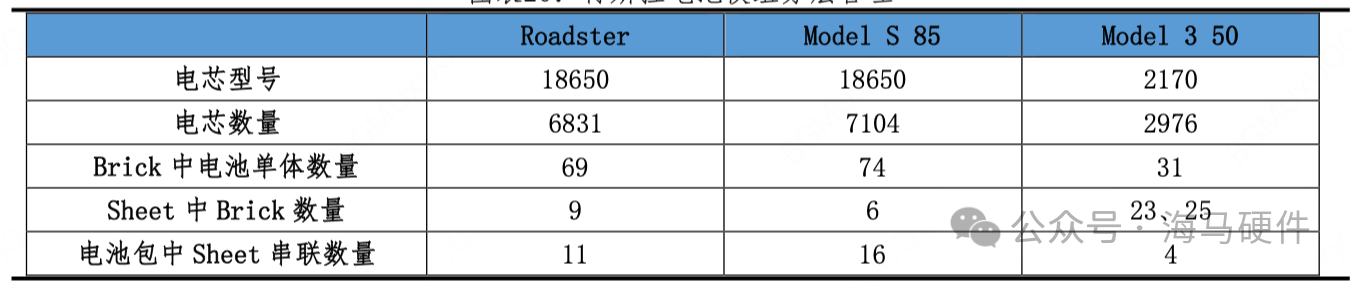

整个体系首要由DVI接口电路、DVI信号解码电路、FPGA及其装备电路、DDR2 SDRAM数据存储电路及DVI信号编码电路组成,体系结构框图如图1所示。

从图1中能够看出,从DVI接口接纳到DVI信号后经过解码芯片SiI1161进行解码,转换成并行的数字信号,然后进入FPGA对四路视频信号进行提取、存储、组成等功用,进行处理后的数据经过编码芯片SiI164再转换为DVI视频信号,就能够接到显现器上显现了。

1.2 软件结构规划

体系的软件规划是体系功用完结的要害。在体系的硬件渠道的基础上,经过对FPGA编程完结对视频解码芯片输出的实时数字视频数据接纳,并依据画面组成需求,对有用视频图画数据进行提取和存储,然后将各路视频数据组成一路输出到显现器。体系完结功用的体系框图如图2所示。

以下要点介绍一下视频信号的提取和组成。

1.2.1 提取模块规划

1)图画提取原理

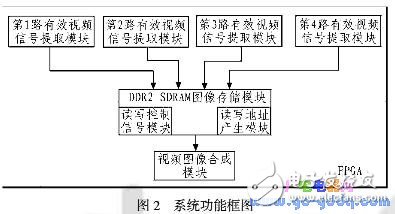

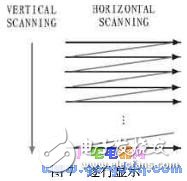

视频画面虽然看起来好像是接连运动的,其实那是一系列停止的图画,这些图画切换得足够快,使得画面看起来像是接连运动的,如图3所示。一种称为场同步(verTIcal sync)的特定时序信息被用于指定新图画从什么时候开端显现;每张停止图画是由扫描线(sCAN line)组成的,即沿着显现器从上到下、一行接着一行进行显现的数据线,另一种称为行同步(horizontal sync)的时序信息用于指定新扫描线什么时候开端显现。

行同步和场同步信息一般经过以下3种办法之一进行传输:

①独自的行同步和场同步信号;

②独自的复合同步信号;

③嵌入视频信号的复合同步信号。

本体系选用的是数字视频,选用的是技能①。

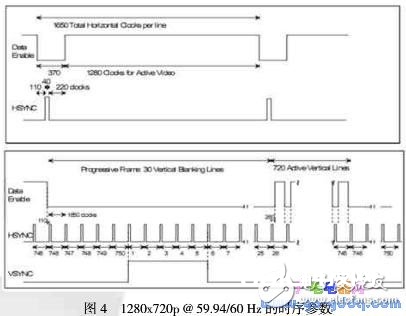

DV支撑超越1 600&TImes;1 200的PC图形分辨率和包括720p、1 080 i和1 080 p的HDTV分辨率,本规划选用的输入分辨率为1 280&TImes;720/60 Hz,像素时钟为74.25 MHz。DVI信号经SiI1161解码后得到带像素时钟的24位并行R、G、B数字信号及H、V、DE信号,它们之间的相互关系如图4所示。

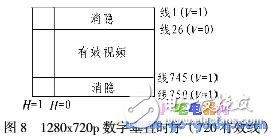

其间,当DE为1时,处理有用视频,当DE为0时,处理HSYNC和VSYNC信号。SiI1161输出的数字视频信号一帧由750行视频数据组成,每一场有用视频行为720行,每一行又有1 650个像素,其间有用像素有1 280个,这些是在视频图画组成进程中要用到的数据,每一个像素都包括R、G、B 3种信号。

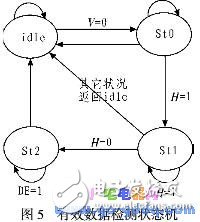

本规划依据H、V、DE信号对有用视频数据进行定位,并依据图画组成的需求把所需的有用视频数据提取出来。在完结的进程中使用状况机来判别有用视频数据,如图5所示。

状况机缺省状况为idle状况。先在idle状况检测场信号由高变低,进入有用数据行,再判别H与DE的凹凸状况,从而检测到有用视频数据,当H由高变低,DE为高的这段视频数据则为有用视频数据。这样则能够依据视频图画组成的需求对视频数据进行挑选提取。

2)图画提取模块规划

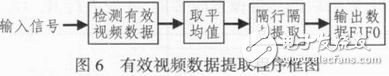

依据上述有用视频数据的提取原理能够提取任何一个数据行或任何一个象素,因为不同的图画组成需求提取的有用视频数是不同的。本规划为四画面切割,需求对每一路输入信号进行1/4紧缩,即需求对有用数据进行隔行隔点提取。有用视频数据提取程序框图如图6所示。

由图可知:接纳到输入信号后,依据视频数据提取原理,检测有用的视频数据,每来一个时钟,接纳一个视频数据存储到RAM模块中;然后对RAM模块中寄存的数据取均匀值;接着对这些均匀值隔行隔点提取,把提取出的数据送入异步FIFO中,便利读写入DDR2 SDRAM中。

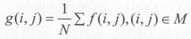

隔行隔点提取有用数据便是要将一些像素丢掉,本规划选用邻域均匀法来改进缩放后的视频图画质量。邻域均匀法的原理是将原图中一个像素值和它周围附近8个像素值相加,然后将求得的均匀值(除以9)作为新图中该像素的值。它选用模板核算的思维,模板操作完结了一种邻域运算,即某个像素点的成果不只与本像素有关,并且与其邻域点的像素值有关。邻域均匀法的数学公式表达为:

其间f(i,j)为给定的图画,经过邻域均匀处理后的图画为g(i,j),M是所取邻域中各附近像素的坐标N是邻域中包括的附近像素的个数。

1.2.2 图画组成和编码模块规划

1)图画组成原理

在像素域的多画面组成中,首要,对原图画按像素进行抽取,分别将多路图画依照必定的份额缩小。然后,依照必定的规则将多路图画进行摆放,摆放后的图画即为多路组成的图画。最终,将组成的图画编码输出,即可在同一个屏幕显现多个画面,完结对多路图画的组成。

组成后的视频图画是逐行显现的,而关于将图画以逐行办法“制作”到屏幕上的设备,每张图画都是从显现器的左上角开端,一向向右移动,直到抵达显现器的右边际停止,然后向下扫描一行,重复地从左到右进行扫描,这个进程一向继续到整个屏幕悉数被改写一次停止,如图7所示。

SiI1161输出的完好的一帧图画数据结构如图8所示。

以四路为例,首要,要分别对原图画进行1/4份额缩小。一帧视频图画有用显现的图画数据为26~745行,则在笔直方向上隔行抽取有用视频行,使笔直方向缩小为本来的1/2。

在水平方向上,每行有用视频由1 280个像素组成,每隔一个像素抽取一个有用视频,使水平方向缩小为本来的1/2。这样经过笔直和水平方向的抽取所得到的图画缩小为原图画的1/4。

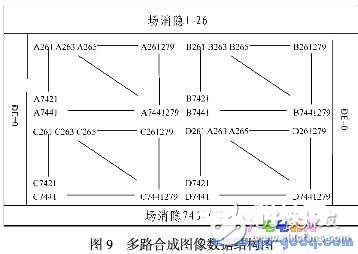

然后,依照一帧图画数据的摆放格局对抽取的各路图画的像素进行摆放。抽取的榜首路图画的行与第二路图画的行组成一整行,第三路图画的行与第四路图画的行组成一整行,四路图画的行组成新的一帧图画的图画数据。

最终,将四路组成图画数据经过SiI164编码输出,经过逐行扫描在一个显现器上显现四路图画,即完结了四路视频图画组成。

2)图画组成模块规划

视频图画画面组成的完结办法首要分为两大类:像素域组成和紧缩域组成。依据体系的图画数据为24位R、G、B数字视频格局,所以在视频图画画面组成中选用像素域内多画面组成的办法。四路视频图画组成的完结进程如下:

首要,分别在笔直方向和水平方向上抽取有用的视频数据,将四路图画各缩小为原图画的1/4。这部分功用由有用视频数据提取模块完结,该模块在前面现已做过具体介绍。然后将提取的各路图画数据按找必定次序摆放,即依照必定的规则存储到DDR2 SDRAM中。各路图画数据的地址依照上一节介绍的地址发生办法完结,都有各自固定的存储空间。

在完结各路视频图画的抽取,存储后,就要对抽取的各路视频图画的进行四画面组成。依据720P体系数字信号的数据格局,把有用视频数据从存储器中选用次序读取出来,在相应的H、V、DE信号的方位,送视频编码输出,完结四路视频图画的组成。在组成的进程中,H、V、DE信号及时钟信号都由榜首路输入的视频信号发生。四路视频组成图画的摆放办法如图9所示。

2 调试成果

经过软硬件的归纳调试,整个视频图画画面切割体系便能够正常作业了。

收集的多路视频图画经过FPGA图画组成处理后,能够在一个显现器显现多路视频图画。

3 结束语

文中选用FPGA开发技能完结了视频图画画面切割器的画面切割的功用。研讨的首要特征在于构建了以FPGA为中心器材的视频画面切割的硬件渠道,经过硬件方式来完结视频四画面切割,图画的提取、存储等都在一片FPGA内完结,进步了体系的集成度,一切的模块规划都是使用Verilog HDL编程完结,和软件完结办法比较,体系在处理速度方面有了明显的进步。输入/输出的信号都为DVI信号,完结了高清视频画面切割。