48 V配电在数据中心和通信应用中很常见,有许多不同的解决方案可将48 V降压至中间电压轨。最简单的方法可能是降压拓扑,它可以提供高性能,但功率密度往往不足。使用耦合电感升级多相降压转换器可以大幅提高功率密度,这种方案与先进的替代方案不相上下,同时保持了巨大的性能优势。多相耦合电感的绕组之间反向耦合,因而各相电流中的电流纹波可以相互抵消。这种优势可以用来换取效率的改善,或者尺寸的减小和功率密度的提高等。本文介绍了一个示例,其磁元件的体积和重量只有原来的1/4,使得1.2 kW解决方案符合1/8砖的行业标准尺寸,并且峰值效率高于98%。本文还重点讨论了如何根据耦合电感的品质因数(FOM)优化48 V拓扑。

48 V配电轨通常会降压至某个中间电压,往往是12 V或更低,然后不同的本地负载点稳压器直接向不同负载提供各种不同的电压。对于48 V至12 V降压调节器,首选之一是多相降压转换器(图1)。这种解决方案提供稳压VO和快速瞬态性能,很容易实现且成本较低。对于几百瓦到>1 kW的功率范围,可以考虑四相并联。然而,高效率通常是一个优先考虑因素,与12 V甚至5 V输入的较低电压应用相比,48 V转换器为了保持低开关损耗,开关频率通常相对较低。这会在”伏特×秒”方面对磁元件造成双重损害,因为已经很明显的电压也会作用相对较长的时间。因此,与较低电压应用相比,48 V的磁元件通常体积较大,并使用多匝绕组来承受显著提高的”伏特×秒”。48 V降压转换器仍然可以实现高效率,但整体尺寸通常相当大,其中电感占据了大部分体积。

基本48 V至12 V ~1 kW降压转换器具有四相,使用6.8 μH分立电感,开关频率为200kHz。这四个电感是目前最大和最高的元件,占解决方案体积的大部分。本文的目标是保持或提高此初始设计所实现的高效率,但显著减小磁元件的尺寸。

常规降压转换器各相的电流纹波可由公式1求出,其中占空比为 D = V O /V IN , V O 为输出电压,V IN 为输入电压,L为电感值,F s 为开关频率。

图1. 使用分立电感的四相降压转换器。

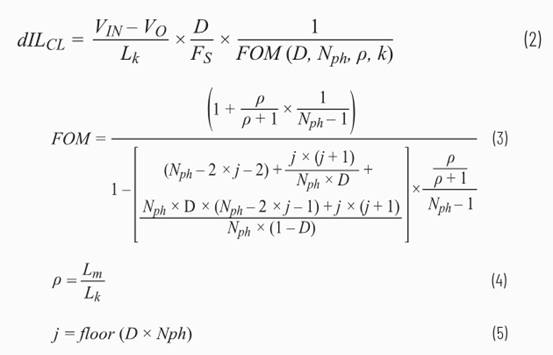

用漏感为L k 且互感为L m 的耦合电感代替分立电感(DL),CL(耦合电感)中的电流纹波可表示为公式2。FOM表示为公式3,其中 N ph 为耦合相数,ρ为耦合系数(公式4),j为运行指数,仅定义占空比的适用区间(公式5)。

CL考虑因素

改进的第一步是针对耦合系数L m /L k 的几个实际合理值绘制 N ph = 4 的FOM曲线(图2)。红色曲线 L m /L k = 0 表示分立电感的FOM = 1基线。已经证明,漏感非常低的陷波CL (NCL)结构一般能实现非常高的 L m /L k ,因此FOM值也很高。然而,虽然在理想情况下目标 占空比正好位于第一陷波D = 12 V/48 V=0.25,但有必要考虑 V IN 和 V O 的某个范围。有时候,标称 V IN 可以是48 V或54 V加上一些容差, V O 可以调整为远离12 V,等等。如果占空比在D = 0.25附近的某个范围内变化,为使电流纹波始终受到抑制,应选择具有相当大漏感的典型CL设计,而不是NCL,但FOM值仍然相当大。假设 L m /L k > 4,与DL基线相比,减小CL中的电感值可能使图2中的FOM提高约6倍。减少能量存储会直接影响所需的磁元件体积。因此,将DL = 6.8 μH降低为CL = 1.1 μH应有利于减小尺寸。

图2. 针对一些不同 L m /L k 值,4相CL的FOM与占空比D的函数关系。突出显示 了目标区域.

图3. DL = 6.8 μH和 CL = 4 × 1.1 μH for (V IN = 48 V 且 F s = 200 kHz)时的电流纹波与 V O 的函数关系。突出显示了目标区域。

图3显示了相应的电流纹波,比较了V IN = 48 V 和 F s = 200 kHz 条件下的基线设计DL = 6.8 μH与建议的4相CL = 4 × 1.1 μH (Lm = 4.9 μH) )。在目标区域中,CL的电流纹波与DL的电流纹波相似或更小。这意味着所有电路波形的均方根相似,传导损耗也相似。相同Fs时的相同纹波还意味着开关损耗、栅极驱动损耗等也相同,因此这两种解决方案的效率应该非常相似(假设DL和CL电感损耗的贡献相似,这是唯一的区别)。

图4. 四个DL = 6.8 μH电感(上方)被替换为CL = 4 × 1.1 μH(下方),体积减小到原来的1/4。

图5. 48 V至12 V调节第一级。元件放置在PCB正面的1/4砖轮廓内。将所有~1 mm 元件移至底部:1/8砖。

图4显示了设计的CL = 4 × 1.1 μH,其取代了四个DL = 6.8 μH电感。5 每个DL的尺寸为28 mm × 28 mm × 16 mm,假设它们彼此间隔0.5 mm,那么尺寸为56.5 mm × 18 mm × 12.6 mm的4相CL可使磁元件体积减小到原来的1/4。图5显示了完整的1.2 kW 48 V至12 V调节解决方案,PCB单面上的元件位于1/4砖轮廓内。CL尺寸和封装经过专门设计,两个CL元件可以安放在行业标准四分之一砖尺寸内。将所有~1 mm元件(FET、控制器IC、陶瓷电容等)放置在PCB底部,从而实现1/8砖尺寸的1.2 kW解决方案。

性能改善

当DL = 6.8 μH电感变为CL = 4 × 1.1 μH时,电感中的电流摆率限制也改善了6倍,这有助于改善瞬态性能。除此之外,尽管磁元件总体积减少到原来的1/4,但100°C时的电感饱和额定值提高了约2倍。

图6显示了建议的 V IN = 48 V 解决方案(输出 V O = 12 V )的瞬态性能。正如所料,对于变化的负载电流,反馈将输出电压调节至预设值,同时补偿输入电压的任何变化。

图6. 75 A负载阶跃下 V O = 12 V 输出(CL = 4× 1.1 μH)时的瞬态性能。

所实现的效率如图7所示,它可能是首要的性能参数。它与先进的行业解决方案进行了比较:48 V至12 V(固定4:1降压)LLC,初级侧和次级侧均有矩阵变压器和GaN FET。10 所实现的满载效率为97.6%,而基准效率为96.3%。这意味着在全功率下损耗减少16.6 W,建议的解决方案实现了1.6倍的改进。当效率已经如此之高时,损耗要降低如此大的幅度通常很难实现。

尺寸和效率之间的权衡当然是可能的。图8比较了CL = 4 × 1.1 μH(磁元件尺寸减小到DL的1/4)和更大的CL = 4 × 3 μH(电感体积仅减小到DL的1/2)的效率。物理尺寸较大的CL = 4 × 3 μH具有较高的漏感 L k = 3 μH 和较大的互感 L m = 10 μH。这使得 Fs可以轻松降低至110 kHz,从而大幅提升整个负载范围内的效率。

图7. 与1/8砖尺寸的先进48 V至12 V解决方案的效率比较。

图8. 使用耦合电感的建议48 V至12 V解决方案的效率与尺寸权衡。

结语

利用耦合电感的优势,48 V至12 V解决方案将磁元件总尺寸减小到基本分立电感的1/4,以行业标准的1/8砖尺寸实现了1.2 kW功率。在磁元件尺寸减小4倍的同时,它保持了出色的效率性能,瞬态电感电流摆率提高了6倍,电感I sat 额定值提高了2倍。

与同样尺寸的业界先进48 V至12 V解决方案相比,它在全功率下的损耗降低了约1.6倍。如果磁元件尺寸的减小幅度可以不那么大,效率还能进一步提高。

同时,建议的解决方案提供出色的稳压输出,可直接放在客户母板上,并利用标准硅FET进一步优化成本。与之相比,采用全GaN FET的非稳压4:1 LLC是作为单独模块制造的,并使用具有多层、敏感布局和嵌入式矩阵变压器的专用PCB。

整体性能改善体现了ADI耦合电感专利IP的优势,我们很高兴将其提供给众多客户用于DC-DC应用。