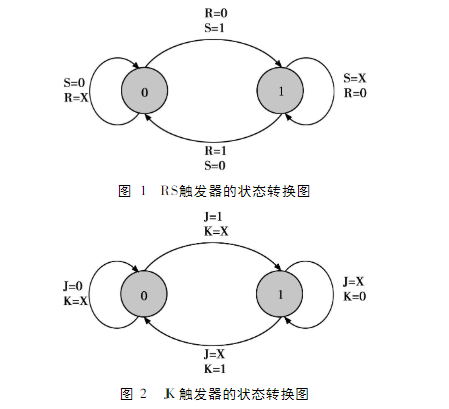

跟着数字集成电路规划的不断扩大及功用的增强,数字电子技术作为一门专业技术根底课程,显得愈加重要。对触发器的描绘有特性表、特性方程式、状况转化图,而触发器的电压波形图既是要点又是难点。例如根本RS触发器。同步RS触发器中的不定态和主从型RS触发器的不定态有何不同,主从型RS触发器和主从型JK触发器的动作特色又是什么。下面就从电压波形图来对RS和JK触发器进行剖析。RS触发器的状况转化图如图l所示。JK触发器的状况转化图如图2所示。

触发器的电路结构和逻辑功用的联系

一、逻辑功用指触发器的次态和现态及输入信号之间在稳态下的逻辑联系,

可用特性表、特性方程或状况转化图表明。

分类:RS触发器、JK触发器、D触发器、T触发器、T/触发器等。

二、电路结构方式不同,动作特色不同。

分类:根本TS触发器、同步RS触发器、主从触发器、边缘触发器等。

三、同一逻辑功用的触发器可用不同的电路结构完成;

同一电路结构方式可作成不同逻辑功用的触发器。

即:逻辑功用与电路结构无固定对应联系。

四、逻辑功用相同而电路结构不同,则是在状况翻转时动作特色不同。

五、JK触发器包含了RS触发器和T触发器的一切逻辑功用。

现在出产的时钟操控触发器定型产品只要JK触发器和D触发器两大类。

JK触发器中

1、令J=S,K=R且J、K不一起为1,约束条件SR=0,构成RS触发器。

2、令J=K=T,则为T触发器。

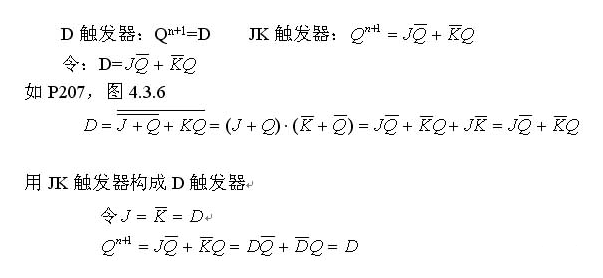

用D触发器构成JK触发器

RS触发器电路剖析

RS触发器的特性由特性表和状况转化图可知,当S=R=1时,其状况均为不定态,而不同电路结构的触发器,其动作特色是有差异的。

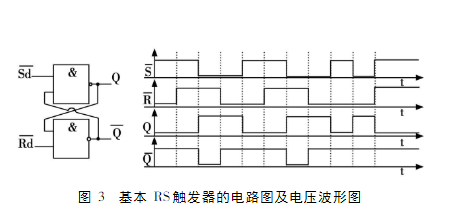

1.1 根本RS触发器

根本RS触发器的电路图及电压波形图如图3所示。

依据对根本RS触发器电路的剖析得知:当SD=RD=0时,Q、均为高电平,一且SD、RD一起变为高电平,Q、输出为O,1(或1,0)无法确认。也就是说当SD=RD=0时,Q和输出端的状况是确认的,即为1,状况不定是指当SD、RD一起从0变成1后,Q、输出端的状况不确认(Q= 1,=0,仍是Q=0,=1,不能确认)。

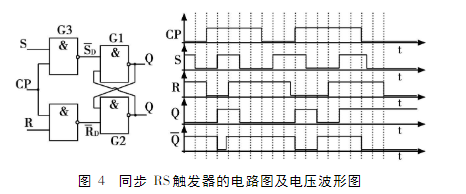

1.2 同步RS触发器

同步RS触发器的电路图及电压波形图如图4所示。

依据对同步RS触发器电路的剖析得知:CP=0时,S=X,R=X,Q、输出端坚持不变;CP=1时,其作业状况同根本RS触发器相同(设Q初态为0)。

CP=1期间,S=R=1,Q和输出一起为高电平1,一旦CP从高电平变为低电平,Q、输出端的状况同样是不定的(即或许Q=0,=1,也或许Q=1,=0)。其输出状况是随机的,无法确认。

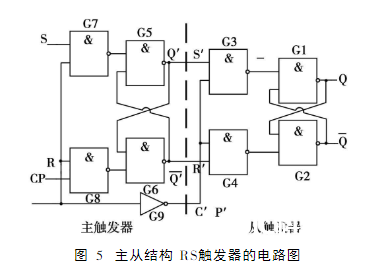

1.3 主从结构RS触发器

主从结构RS触发器的电路图如图5所示,由主触发器和从触发器组成。

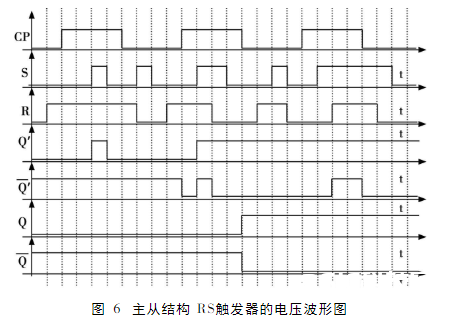

主、从触发器分别由两个同步RS触发器组成。依据对主从型RS触发器电路的分新,画出其相应的电压波形图,主从结构RS触发器的电压波形图如图6所示(设初态为0)。

CP=1时,主触发器触发作业,从触发器的Q、输出端坚持不变;CP=O时,从触发器触发作业,主触发器的Q’、输出端坚持不变。输出端输出状况的改动发生在CP信号的下降沿,但却是遭到CP=1期间R、S输入信号的影响。图4中的脉冲3,CP=1,S=R=1时,Q’==1,且继续到CP下降沿时间,则Q’=0,=1,仍是Q‘=1,=0不确认。所以当CP下降沿时间一到从触发器Q端输出高电平仍是低电平无法确认,其状况不定,并不是指Q、一起输出高电平,和根本RS、同步RS触发器的了解不同。

经过对电路的剖析总结出主从型RS触发器Q端电压波形改动的描绘办法。

从触发器是依照CP下降沿时间到这一时间主触发器输出端Q’、的信号触发作业。即Q’=1,=0,则Q=1,=0;Q‘=0,=1,则Q=0,=1。所以不需求对CP=1期间,主触发器Q’、的信号悉数剖析出来。能够在每个CP脉冲下降沿到来这一刻往前去确认Q’、,一旦清晰知道Q’、的信号,就不需求知道前面Q‘、的信号,即知道CP下降沿这一时间的Q’、的信号,则CP下降沿时间一到,从触发器的输出也清晰了。

图4中脉冲1下降沿t2时间到,怎么判别Q端的信号?因为t1-t2期间S=O,R=1,主触发器量0,即Q’=0,=1,所以t2时间一到,Q=Q’=0,==1,不需求对t1之前的信号再进行详细剖析。

同理脉冲2下降沿t5时间到,因为t4-t5期间,S=R=O。主触发器处于坚持状况,而Q’、坚持什么状况不清楚,再看t3-t4期间,S=1,R=0,主触发器置1,使Q’=1,=0,由此可知t4-t5期间主触发器坚持1状况,所以在t5时间一到Q=Q’=1,==0。

2 JK触发器电路剖析

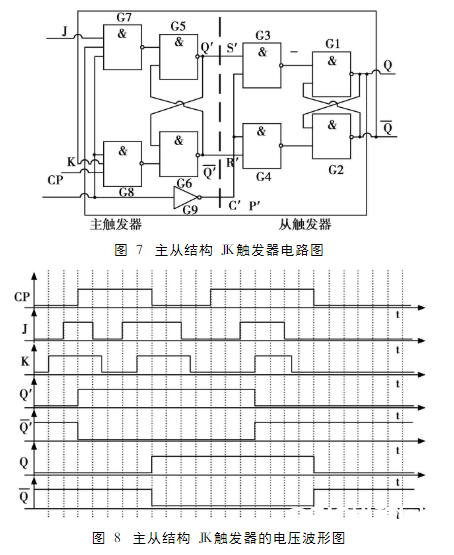

主从结构JK触发器和主从结构RS触发器差异在于当J=K=1时,触发器将翻转为与初始状况相反的状况,所以JK触发器不再存在输出状况不定的状况。主从结构JK触发器电路图如图7所示。图8为主从结构JK触发器的电压波形图(设初态为0)。

脉冲1:当CP=1时,t1-t2期间J=K=1,Q’取反,由本来的0取反为1。主触发器的状况改动了一次不会再翻转回来,所以t2-t3期间,虽然j、k输入端的信号发生改动,却不必再详细剖析,t3下降沿时间一到,从触发器Q端亦从0翻转到1。脉冲2:当CP=1时,t4-t5期间,J=K=0,为坚持不变状况,状况没有改动,故需求对下一时间段进行剖析,t5-t6期间,J=1,K=O,主触发器量1,而原状况就为1,状况没有发生改动,所以还需对下一时间段进行断定,t6时间一到,J=K=1,主触发器输出状况,取反为0,因为主触发器的状况只能改动一次,所以不需求再剖析后边的时间段,下降沿t7时间一到,从触发器随从主触发器—样输出低电平。

3 电压波形图

经过对不同电路结构触发器电压波形图的剖析,发现仅了解触发器的特性表,特性方程式,状况转化图是不行的,还需了解其电路结构才干真实把握触发器电路。并由此得到主从型RS触发器和主从型JK触发器电压波形图的描绘办法。

主从型RS触发器:判别每个CP下降沿时间届时状况的改动,是自这一时间起自后往前断定,CP=1期间,主触发器的状况,一旦主触发器的状况清晰了,就不需再往前断定主触发器的状况,该状况即为CP下降沿届时主触发器的状况,而从触发器在CP下降沿时间一到跟从主触发器的状况改动即可。

主从型JK触发器:判别每个CP下降沿届时输出状况的改动,是从CP为高电平开端(即上升沿这一时间)依据J、K输入端的信号改动自前往后分时间段断定主触发器的状况,—旦状况改动了一次,就不需求再剖析后边的输入信号,因为CP=1期间,主触发器的状况只能改动一次,此状况保持到CP下降沿届时,从触发器跟从主触发器的状况而改动。

4 结束语

触发器作为构成数字体系的一种根本逻辑单元,因为其不同的电路结构带来不同动作特色,在电路设计和运用时,须差异运用。而在介绍触发器这一章时,因为是从组合逻辑问题过渡届时序逻辑问题,对触发器电路的剖析及描绘办法和组合逻辑电路不同,故需对不同电路结构的触发器,在剖析其电路结构的根底上,总结出其动作特色和规则,以便正确把握和运用触发器。

在实践的电路中,一般运用触发器,经过时钟脉冲进行操控,用得最多的时D触发器和J-K触发器;触发器能确保一个脉冲内的信号安稳。当然,也存在其它类型的触发器(如T触发器和T’触发器等)。

触发器和组合电路中的译码器、编码器、选择器、分配器等组合在一起能构成一切咱们需求的电路,这也是后续课程如计算机组成原理和嵌入式等课程的根底,紧记并了解组合电路和典型触发器的功用特性是进行后续课程学习确保。