摘要:规划了一种可进行实时视频收集、紧缩和传输的视频收集处理体系。该体系充沛结合FPGA和ARM的硬件优势,完结了设备接口和视频信号处理的全数字化,易与信号处理新技能相结合,体系结构紧凑,体积细巧、呼应快速;依据FPGA的前端处理更增加了图画处理算法晋级的灵敏性,适用于工业长途监控等多种场合。

要害词:图画传感器;FPGA;视频紧缩;ARM;以太网

Abstract: To collect data in high speed and be simple in the structure, a Video Acquisition and Processing system with real-time compressing and transmission is presented. The selection and interface of components, and the function realization of FPGA and ARM are discussed. The design of some key modules,such as the driver of the cmos sensor, and the convection and compressing process of data, and the design of transport via Ethernet are introduced.

Key words: Image Sensor; FPGA; Video Compressing; ARM; Ethernet

近年来,视频技能的飞速发展,使得视频产品越来越遍及。视频信号收集是整个视频运用的前端部分,扮演着极其重要的效果。传统的图画收集卡面向核算机运用,体积大,可靠性有待进一步进步,所以便发生了一些新的视频收集办法,这些计划有的依据FPGA和DSP,有的依据ARM和编码芯片,在实时性、灵敏性、 可维护性方面各有千秋。本文针对FPGA在数字信号处理速度上的优势以及ARM在操控方面的利益,规划了一种全数字化的实时视频收集体系,具有很有用的参考价值。

1 体系构成

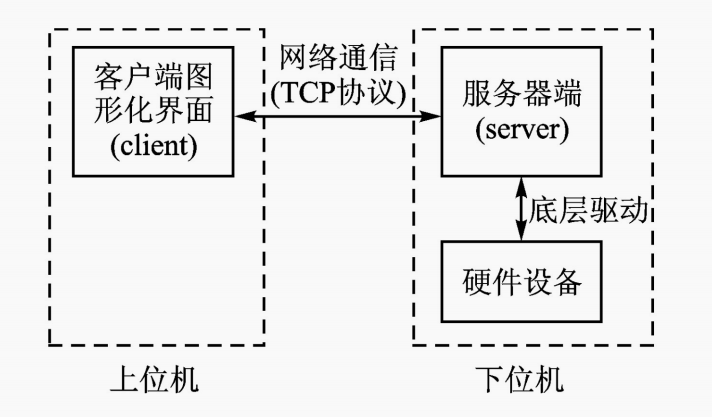

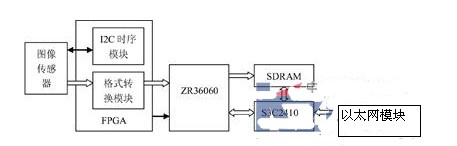

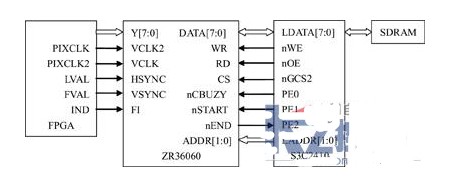

本体系的结构框图如图1所示,图画传感器模块担任图画收集,FPGA发生I2 C时序操控CMOS图画传感器芯片,并将收集到的图画数据进行相应处理后送到紧缩芯片ZR36060进行紧缩;ARM担任紧缩芯片的驱动、以太网芯片的操控和UDP/IP协议的完结,以及视频收集体系的指令操控和数据传输, 以太网模块首要完结以太网数据传输。SDRAM做数据暂存与ARM存储空间的扩展,收集到的视频图画以帧为单位经过网卡芯片传送到网络。

图 1

2 硬件规划

2.1 图画传感器

图画传感器选用M%&&&&&%RON公司的MT9M131。它是一种五颜六色CMOS图画传感器,可支撑SXVGA、VGA、QVGA等显现格局,I2 C总线接口,最大支撑分辨率1280*1024,在VGA格局下可到达30帧/每秒的收集速度,并具有主动曝光操控、主动增益操控、主动白平衡、主动带通滤波、主动黑级校准等功能。本体系选用VGA格局,CMOS传感器的操控时序由FPGA发生。

2.2 FPGA器材

FPGA器材的首要功能包含图画传感器的操控、收集后的图画数据处理和格局转化,为了收集到质量更好的图画,将来还会在此部分参加一些相应的处理算法。因而,为确保体系的实时性,体系选用了Altera公司Cyclone II系列的EP2C35F672C6。该芯片具有35000个逻辑单元、672个引脚、475个用户自定义I/O接口、35个嵌入式乘法器和4个锁相环,完全能够满意体系要求。

2.3 ARM处理器和网卡芯片

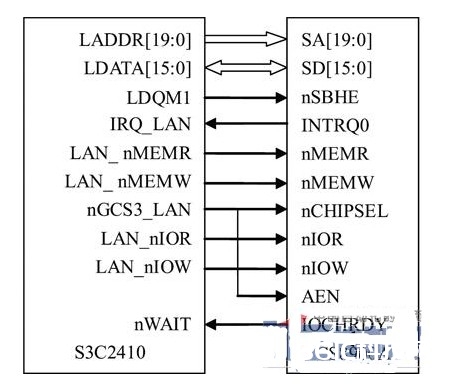

ARM处理器选用三星公司的S3C2410,该处理器具有独立的16KB指令Cache和16KB数据Cache,MMU,支撑TFT的LCD操控器,NAND闪存操控器,3路串口,4路DMA,4路带PWM的时钟,最高可运行在203MHz。体系选用的网卡芯片是CS8900A,它是用于嵌入式设备的低成本以太局域网操控器。它的高度集成规划使其不再需求其它以太网操控器所必需的贵重外部器材。

CS8900A包含片上RAM,10Base-T传输和接纳滤波器,以及带24毫安驱动的直接ISA-总线接口。除了高度集成,CS8900A还供给其它功能和装备挑选。它共同的PacketPage结构可主动习惯网络通信量形式的改动和现有体系资源,然后进步体系功率。图2为网卡芯片与S3C2410的接口示意图。

图 2

2.4 视频紧缩芯片

JPEG编解码芯片ZR36060是专为视频收集与修改运用而规划的,能够便利地完结对视频信号的实时紧缩宽和紧缩。在进行紧缩时,ZR36060承受 YUV4:2:2数字视频信号,将其编码为JPEG码流输出。ZR36060对像素块和CCIR视频信号可完结高达25~30帧/秒的紧缩;灵敏的数据接口,支撑三种YUV视频接口形式,即8位主形式、16位从形式和8位从形式;3种不同的比特率操控形式用于停止和运动视频的紧缩;能够和多种常用视频解码器完结无缝衔接[1]。据统计,JPEG格局的紧缩份额约为70~80:1,而本体系中选用的分辨率并不高(640*480),直接运用ZR36060进行帧内编码紧缩能够满意要求,一起也减少了FPGA部分的开发作业量。

3 要害模块的作业原理

3.1 图画传感器驱动

MT9M131是规范的I2 C总线器材,接口简略,传感器作业时只要6个操控信号。其间MCLK由FPGA发生,是传感器作业时钟输入;FVAL是帧有用信号,它的上升沿表明一帧数据的开端。在FVAL信号的有用期间内包含了480个行有用信号LVAL,而每个LVAL信号的高电平期间包含了数据总线上640个像素数据的输出。所以,在FVAL一个周期内,图画传感器正好输出了完好的一帧图画。分辨率为640×480。仅当FVAL和LVAL信号一起为高电平时,传感器输出数据 D[9:0]有用,FPGA在每个像素时钟PIXCLK上升沿时将有用数据读入。经实测,传感器正常作业时,SCLK,LVAL频率约为7.56kHz和 14.2kHz。

本体系选用Verilog HDL言语来编写CMOS图画传感器的时序驱动。在实践规划中,把操控模块分红两部分:I2C_Config模块依据设定的曝光时刻来发生I2 C总线SCLK和SDAT时序,而Capture模块则担任与传感器的数据接口,读入10位的图画数据,并送到下一级模块进行相应处理。以下是 Capture模块部分代码:

always@(posedge iCLK or negedge iRST)

begin

if(!iRST)

……… //各信号清零复位

else

begin

Pre_FVAL = iFVAL;

if( ({Pre_FVAL,iFVAL}==2’b01) mSTART )

//当时帧有用且前一帧处理完

mCMOS_FVAL = 1;

else if({Pre_FVAL,iFVAL}==2’b10) //正

在处理前一帧

mCMOS_FVAL = 0;

mCMOS_LVAL = iLVAL;

mCMOS_DATA = iDATA;

//读取数据送入FPGA

if(mCMOS_FVAL)

//帧有用

begin

if(mCMOS_LVAL)

//行有用

begin

if(X_Cont639)

X_Cont =X_Cont+1;

else

begin

X_Cont =0;

Y_Cont = Y _

Cont+1; //核算像素坐标,便利后续模块显现

图 3

3.2 格局转化模块

从数字图画传感器传来的原始图画质量,在整个体系的功能影响中占首要位置,对后续的视频紧缩和传输速度有着非常重要的影响。后期将会在收集前端参加相应的图画处理算法。而大多数处理算法都是依据RGB颜色空间的,为了进行视频紧缩以减小数据量,就需求进行RGB到YUV的颜色转化。

YCbCr是YUV归于颜色空间的一种贮存格局,适用于MPEG、JPEG等格局的编码。比较RGB颜色空间,YCbCr颜色空间有一个显着的长处。Y的存储能够选用和本来画面相同的分辨率,可是Cb,Cr的存储能够运用更低的分辨率。这样能够占用更少的数据量,并且在图画质量上没有显着的下降。所以,将颜色信息以低于测量信息的分辨率来保存是一个简略有用的图画紧缩办法。

在ITU-R BT.601规范中,主张在核算Y时,权重挑选为kr=0.299,kg=0.587,kb=0.114。所以常用的转化公式如下:

Y=0.299R+0.587G+0.114B

Cb=0.564(B-Y)

Cr=0.713(R-Y)

选用硬件描绘言语进行编程之前,需求消除浮点数运算。合理使用硬件资源是编写代码时要充沛考虑的。关于常系数乘法单元,其占用的LEs(Logic Elements)与系数巨细有关。为了防止呈现负数和溢出问题,终究选用的转化公式如下:

Y = [CA*27] *(R – G)+ G + [CB*27] *(B – G)+ YOFFSET

Cb = [CC*27] *(B – Y)+ COFFSET

Cr = [CD*27] *(R – Y)+ COFFSET ([ ]符号表明取整运算)

各参数的取值见表1[2]。

表1 各参数值

CA0.299 CC0.492

CB 0.114CD0.877

YOFFSET 16 COFFSET 128

3.3 图画紧缩操控

ZR36060的操控接口示意图如图3所示,VCLK和VCLK2是需求外部供给的时钟信号,由FPGA发生的PIXCLK为25MHZ,满意体系要求。 VCLK是VCLK2的分频,并要求与VCLK2同步。

本体系挑选ZR36060作业状况为:8位代码从形式,视频同步从形式,8位视频总线宽度。ZR36060的接口可分为视频接口、主机接口和代码接口三部分。视频信号由视频接口Y[7:0]输入,主机接口经过DATA[7:0]对芯片内部寄存器设置,操控作业状况,紧缩后的码流经过代码接口 CODE[7:0]输出到存储器中缓存。8位代码从形式下,主操控器的数据总线DATA[7:0]经过读写HostData对ZR36060的内部寄存器进行设置和读取,代码总线CODE[7:0]从CODEFIFO读写JPEG数据。行同步信号HSYNC接到图画传感器的LVAL引脚,场同步信号 VSYN接到传感器的FVAL引脚。奇偶场指示信号由FPGA给出,每收集到FVAL的上升沿,IND信号翻转一次,以指示奇偶场。

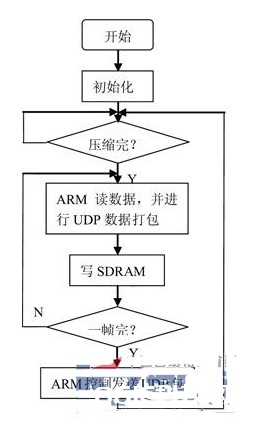

3.4 以太网数据传输

本体系选用UDP/IP协议来完结图画数据的网络传输。紧缩后的图画数据经ARM进行UDP数据打包后,存储在SDRAM中。一个完好的数据帧格局包含以太网头、IP头、UDP头和一行图画数据,其体系作业流程图见图4所示。ZR36060 每紧缩完结一帧,就由S3C2410读取并写到SDRAM中,然后判别是否读完一帧图画数据,读完后则发送UDP包,将图画数据经过以太网发送到网络。

图 4

4 小结

本文提出了一种依据FPGA和ARM的视频收集处理体系,其特色在于设备接口和视频信号处理的全数字化,体系结构紧凑,体积细巧、呼应快速;依据FPGA的前端处理更增加了图画处理算法晋级的灵敏性,适用于工业长途监控等多种场合。后期还可在收集端参加相应的图画处理算法,以进步图画质量。

参考文献:

[1] 陈晓敏, 王学进, 王志华, 张利. JPEG 编解码芯片ZR36060在长途视频监督体系中的运用[J]. 电子技能运用, 2006. 10.

[2] 魏博, 肖文, 王丛琳, 戎路. 依据FPGA 的CMOS 图画传感器的驱动开发[J]. 光学与光电技能, 2008, 10: 56-58.

[3] Gabor Szedo. Color-Space Converter: RGB to YCrCb. Xilinx Corp, 2006.

[4] 吴继华, 王诚. Altera FPGA/CPLD规划[M]. 人民邮电出版社, 2005.