超声波检测作为一种常用的无损检测技能之一,具有穿透力强、设备简略、检测灵敏度高、运用方便和安全性好的长处,在产品质量操控、结构完整性评价、部件剩下寿数猜测等范畴有着广泛的运用。它运用资料自身或内部缺点的声学性质对超声波传达的影响,非损坏性地勘探资料内部和外表的缺点巨细、形状和散布情况。跟着计算机技能和高速器材的不断发展,超声波信号的数字化收集和剖析逐渐替代了传统的超声探伤方法,而大规模集成电路与嵌入式操控技能的发展为规划高速、高可靠性、低功耗和低本钱的超声信号收集计划供给了可能性。

本文将FPGA技能和DSP单片体系规划技能结合起来,规划了一种新式四通道超声探伤数据收集处理体系,由FPGA合作DSP并行地进行数据收集、处理和存储作业,较好地处理了体系体积、功耗和处理速度等方面的对立。

1 体系整体规划计划

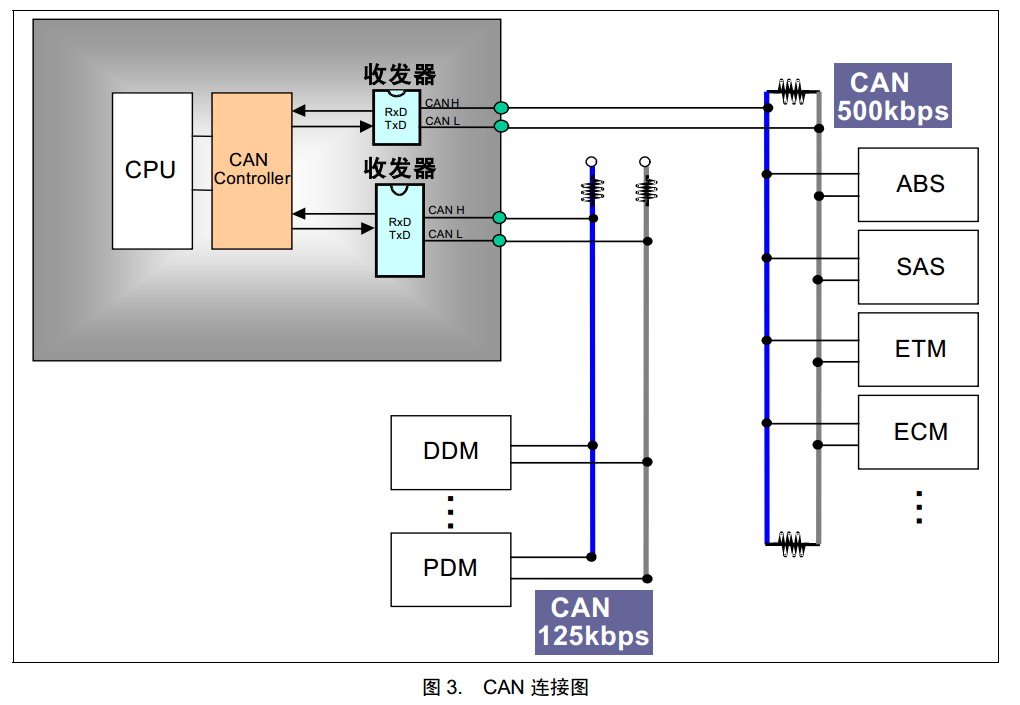

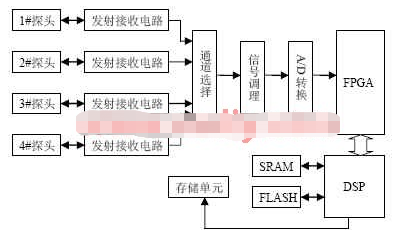

所规划的依据FPGA的数字化超声探伤数据收集处理体系首要包含超声发射接纳单元、信号调度单元(包含扩大、检波、滤波)、模数(A/D)转化单元、数据缓冲处理单元、数据存储单元。其电路根本构成如图1所示:

图1四通道数字超声探伤数据收集处理电路原理图

中心处理器DSP选用的是TMS320VC5402。该芯片是TI公司TMS320VC54X系列的DSP芯片,是为完结低功耗、高性能而专门规划的DSP芯片,首要运用在通讯、数据收集等体系中。该芯片选用CMOS制作工艺,归于第七代DSP产品,它的作业频率可以依据需要进行调整。FPGA挑选一片美国ALTERA公司的APEX20K系列EPF20K300EQC240-1,它有300000的门阵列资源,240个管脚,152个I/O口,输入输出电压可以兼容5V、3.3V、2.5V,运用VHDL言语进行编程操控。

超声波探伤回波具有准周期特性,A/D器材对波形的采样实际上只需要很少的一段时刻。依据这一特色,咱们选用了多通道时分复用技能。这一技能的中心思维是经过对模仿开关(MAX4141)的操控,顺次对4个通道超声波触发和数据采样,降低了体系本钱,简化了体系的操控电路。发射电路的激活是由FPGA来完结的,当FPGA输出的同步操控脉冲加在某一发射电路上时,该发射电路便开端作业。超声发射电路首要用于发生高压窄脉冲信号(400V),此高压窄脉冲信号加载在超声探头的压电晶片上,将电能转化为声能(机械能)而发生超声波信号。回波信号经过通道挑选开关后,进行信号扩大与滤波,然后在FPGA的操控下进行A/D转化。选用一片高速ADC器材,顺次完结各路数据的收集,收集的数据在FPGA内紧缩处理后存入其内部的双端口RAM中,然后由微处理器读取数据,然后存储到硬盘中待剖析。

2 信号调度电路

信号调度电路首要包含对射频信号的检波和前置滤波以及扩大或衰减等。因为探头输出的缺点信号很弱,现场的作业环境又很杂乱,电源搅扰、电磁辐射搅扰很严重,因而对扩大器的质量要求很高,挑选AD公司AD603作为衰减器的首要器材。AD603具有线性分贝、噪声低、频带宽、增益精度高、增益操控灵敏等特色。选用三级扩大,第1、2级扩大器的增益规模为-10dB-30dB,第3级的增益规模为10dB-50dB,这样衰减器增益在-10dB-110dB规模内改变,可以完结最大120dB的衰减量。扩大器的增益由计算机输入的增益操控信号完结主动调理。

3 A/D采样操控

作为数据收集的要害部分,ADC芯片选用的是美国MAXIM公司出产的MAX1449芯片,该芯片是一种10位、105MSPS、单3.3V电源、低功耗的高速A/D芯片,选用差分输入,带有高宽带采样/坚持的10阶段流水线型结构,采样信号每半个时钟周期经过一个流水线段,完结接连转化到数据输出共需5.5个时钟周期。每次转化成果都被输入高速缓冲存储器。在A/D转化期间,高速缓冲存储器的数据线和读写信号由FPGA内部的采样逻辑操控单元发生。

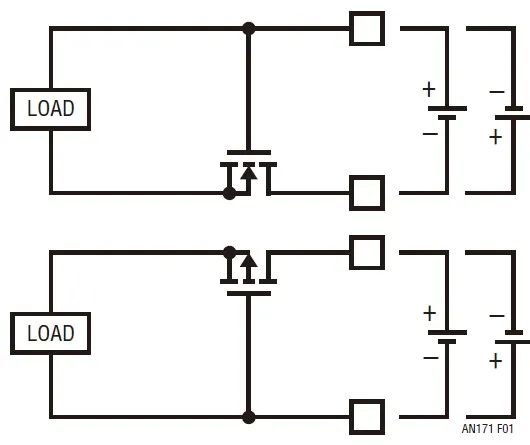

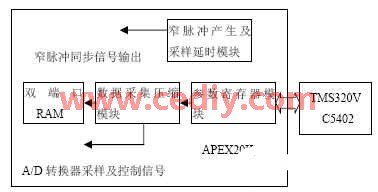

4 FPGA与DSP功用接口规划

对DSP而言,FPGA是DSP的外部I/O端口,由地址和I/O读写信号译码发生相应的输入输出操控指令或对相应的端口寄存器进行操作。FPGA与微处理器的接口首要是用来为FPGA传递操控参数。比方,每一收集过程中的采样点数、采样点紧缩比率、延时参数、增益值等。操控参数的传递,使得该套体系可以适用于不同波形收集的要求,然后完结了智能化。FPGA在内部经过对数据进行紧缩处理今后,将有用的波形数据信息逐一存储于外部双端口RAM中,以供数据存储运用。

图2 FPGA与DSP功用接口

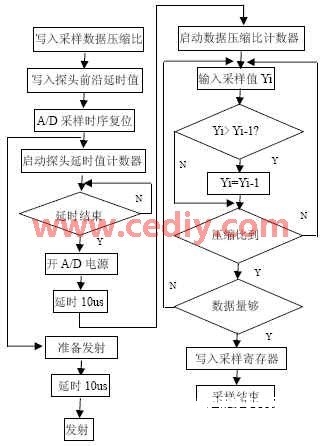

5 数据紧缩处理

数据紧缩处理是对射频信号高速采样后进行前置处理的重要环节之一,需要在坚持超声回波信号根本特征前提下对采样数据进行在线紧缩。并且要求紧缩后的数据与原始采样信号的包络相吻合,为此,咱们在每次紧缩过程中,只取采样所得的最大值,而放弃其它采样值。数据紧缩电路首要由紧缩比的存储与计数,采样前探头前沿的延时存储与计数,采样操控,采样比较与锁存,紧缩比值计数,时序操控等电路组成。CPU将计算所得采样数据紧缩比、探头前沿延时计数值等数据送入数据紧缩电路中相应的锁存器,然后宣布时序复位指令,发射,发动探头延时计数,延时到后发动A/D采样,一起紧缩比计数电路开端计数,在时钟信号的操控下,每采样一次,紧缩比计数器减1,并将当时采样值与前次采样值比较,如大于则保存,不然放弃,直至紧缩比计数到零后得到一个有用的采样数据。一起紧缩比计数器主动复位,重新开端计数。其作业流程如图3所示。

图3数据紧缩软件流程图

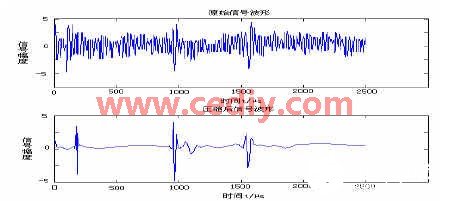

6试验成果

超声波探伤仪选用中心频率为10MHz探头、100MHz采样频率对一块含有人为缺点的试块进行了A方法扫描,将原始数据和紧缩后数据保存下来,对原始信号波形(含噪声)和终究紧缩处理后的信号波形作了比照,如图4所示。可以发现,紧缩后的数据可以很好的保存原始信号中的缺点信息,满意了实际需要。

图4超声探伤信号处理前后比照

本文作者立异点:选用了多通道时分复用技能,规划了一种依据DSP+FPGA结构的四通道数字超声检测体系,在对波形收集的一起完结数据的紧缩,紧缩后的数据在时刻上是均匀散布的,既保存了波形的形状,又确保峰值点不丢掉,为探伤成果的后续剖析奠定了根底。

责任编辑:gt