一、体系全体介绍

本体系是依据FPGA的多路CameraLink数据的单光纤传输规划,因为FPGA的开发本钱低价,晋级便利所以成为该体系规划的挑选。

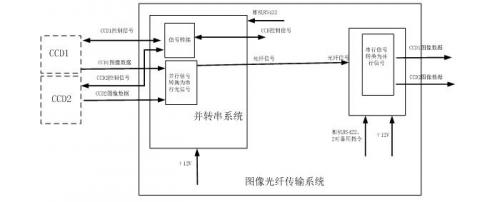

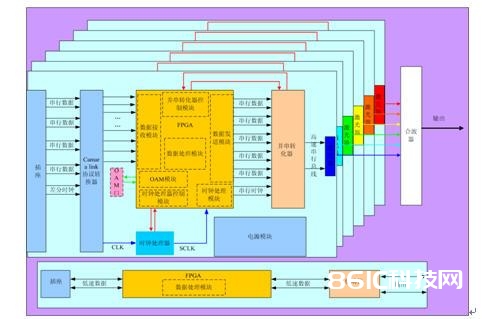

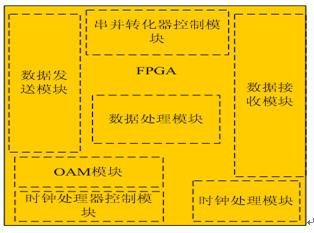

图画光纤传输体系首要由并转串体系和串转并体系组成,体系组成的框图如图1.1所示。

并转串体系将两台CCD的并行图画数据转化为串行光信号,经光纤传输后发给串转并体系,串转并体系将光信号再康复成两台CCD的并行图画数据。光纤上传输的图画数据速率在1.4G-2.8G内可调。

图1.1体系组成的框图

二、体系作业原理和组成

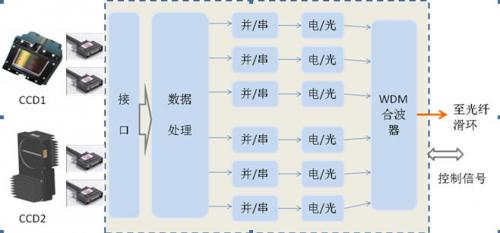

依据本钱和完结难度的考虑,首要的作业原理是选用电路并串改换+光波分复用(WDM)的方法完结超大容量数据组成,完结数据通过一根光纤传输的功用。也便是先将每一组Camera link 数据进行并串改变,构成一路串行信号,之后通过WDM技能将各路串行信号的各个波长通过光路组成到一根光纤傍边,通过传输后(首要是通过光纤),在接纳端还原成各个波长,通过处理后康复出原始信号。

体系根本组成如下图所示。两个可以full装备的CCD摄像头别离通过两条26芯标准电缆将图画数据传给本体系。每个Camera Link数据组X、Y和Z别离通过接口进入体系,并完结并串转化、电光转化、合波等,最终统一到一根光纤。通过光纤传输后,再由接纳部分通过火波器、光电转化、串并改换和输出接口后,康复为同从CCD接纳到的原始数据彻底相同的格局,再通过四条26芯标准电缆将数据输出给下级处理设备。

图2.1 体系组成框图

三、完结计划

3.1全体思路

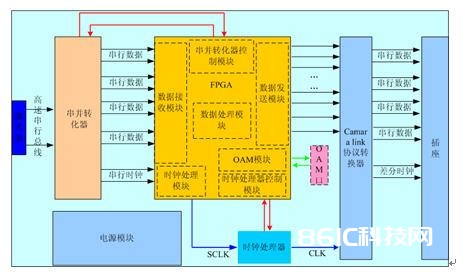

图3.1 体系计划框图

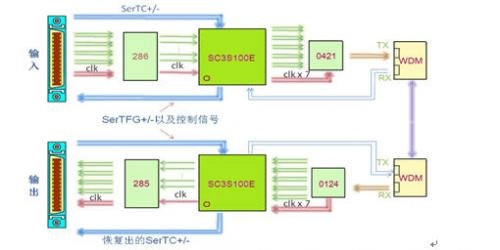

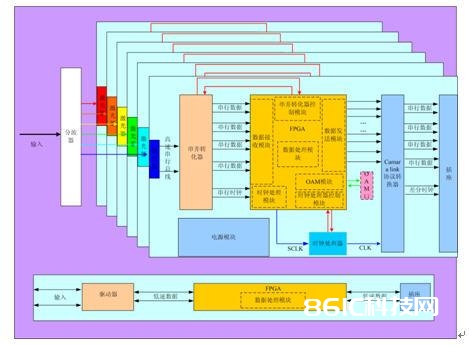

体系选用电路串并改换+光波分复用(WDM)的方法完结超大容量数据组成的方法,完结数据通过一根光纤传输。体系的构成如图3.1所示。

体系分为发送部分单元和接纳部分单元。发送部分单元和承受部分单元又各分为高速部分模块和低速部分模块两部分。高速部分模块独立完结数据的串化、解串化作业;低速部分模块完结相关数据和操控信号的处理。

发送部分单元高速电路完结六路Camera link 总线(两个CCD full装备的数据量)的串化,把每一路camera link 总线的数据串化后,送入激光器变成光信号,再用波分复用的方法通过一根光纤传送出去。发送部分全体框图如图3.2所示。

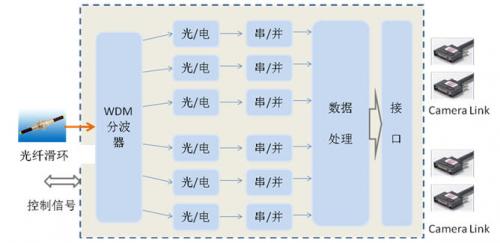

图3.2 发送全体框图

接纳部分单元高速电路完结六路camera link 总线 (两个 CCD full装备的数据量)的解串作业,首要通过波分化复用体系分出每一路camera link 总线的数据,然后再把每一路串化的camera link 数据解串,康复成标准的并行信号。接纳部分全体框图如图3.3所示。

图3.3 接纳全体框图

在体系地评价产品的杂乱性和可靠性的需求后,咱们决议选用Xilinx Spartan3E系列产品作为FPGA中心模块的首选器材。Xilinx 3E系列产品价格较低,功用全面,是世界上热销的 FPGA。

3.2发送部分单元

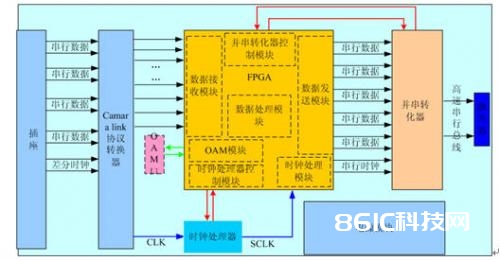

发送部分单元高速电路完结六路Camera link 总线(两个CCD full装备的数据量)的串化,把每一路camera link总线的数据串化后,送入激光器变成光信号,再用波分复用的方法通过一根光纤传送出去,发送单元电路模块全体框图如图3.4所示。

图3.4 发送单元电路模块全体框图

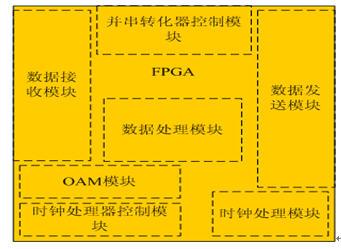

发送单元包含如下几个模块,如图3.5所示:

-

发送单元数据接纳模块:完结正确接纳来自Camera link 协议转化器的数据的功用;

-

发送单元数据处理模块:完结发送数据的中心处理功用;

-

发送单元数据发送模块:完结正确将组成的数据以和Serdes匹配的方法发送到serdes的功用;

-

发送单元并串转化器操控模块:完结对并串转化器的OAM功用;

-

发送单元时钟处理模块:有用内部的时钟部件完结时钟的相应处理,比方分频、倍频、相位调整等;

-

发送单元时钟处理器操控模块:完结对时钟处理器的OAM的功用;

-

发送单元OAM模块:和上层操控办理器协作,完结发送体系的OAM作业。

图3.5 发送单元模块区分

下面详细介绍发送部分单元模块详细功用及完结:

-

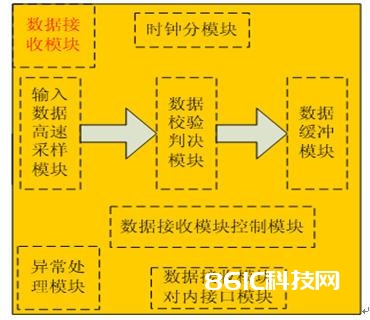

发送单元数据接纳模块完结数据的正确接纳、断定和缓冲的功用。模块内部逻辑框图如图3.6所示。包含输入数据高速采样模块、数据校验断定模块、数据缓冲模块、数据接纳模块操控模块、数据接纳模块对内接口模块、反常处理模块和时钟分模块。

图3.6 发送单元数据接纳模块内部逻辑框图

数据缓冲模块:对数据校验断定模块发生的数据进行缓冲,进步数据的可靠性和体系的安全性,呈现溢出或许闲暇的时分上报相关信息给数据接纳模块操控模块便于OAM。

反常处理模块:供给不行猜测的反常处理,比方复位等,以进步体系的可靠性和安稳性。

时钟分模块:供给本模块需求的时钟。反常处理模块不需求时钟;数据接纳模块对内接口模块时钟为OAM模块作业时钟;数据接纳模块操控模块为异步,不需求时钟;输入数据高速收集模块和数据校验断定模块选用线路时钟的3倍频或许6倍频时钟;数据缓冲模块选用线路时钟的频率。

-

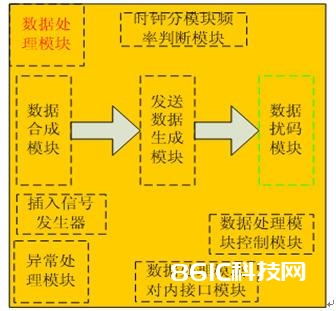

发送单元数据处理模块完结中心的数据发生的功用。模块内部逻辑框图如图3.7所示。包含刺进信号发生器、数据组成模块、发送数据生成模块、数据加扰模块、数据处理模块操控模块、数据处理模块对内接口模块、时钟分模块和反常处理模块。

图3.7 发送单元数据处理模块内部逻辑框图

刺进信号发生器:发生定帧信号,2bit定帧信号发生的原理和方法需求和OAM模块协作完结。

数据组成模块:把28位数据信号和相应的2bit定帧信号兼并,成为30bit的帧结构。

发送数据生成模块:依据camera link 总线的时钟频率断定是否对数据进行double处理,处理后的数据为真实的发送数据。

数据加扰模块:该模块首要完结加扰进程,确保发送数据中有足够的时钟信息。

操控模块:完结对模块内部各个分模块的监测和办理,并通过数据处理模块对内接口模块和OAM模块进行相关的数据沟通,承受OAM模块的办理。

时钟分模块:为内部各个分模块供给时钟。

反常处理模块:供给不行猜测的反常处理,比方复位等,以进步体系的可靠性和安稳性。

-

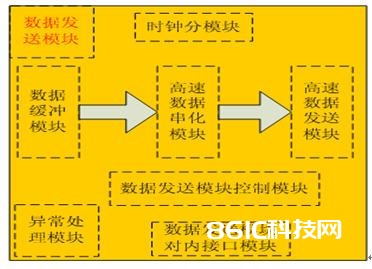

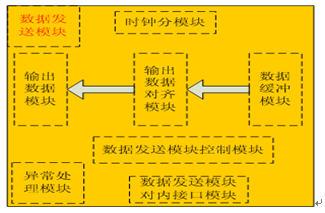

发送单元数据发送模块

发送单元数据发送模块完结数据缓冲、高速数据串化和高速数据发送的功用。模块内部逻辑框图如图3.8所示。包含数据缓冲模块、高速数据串化模块、高速数据发送模块、数据发送模块操控模块、数据发送模块对内接口模块、反常处理模块、时钟分模块

图3.8 发送单元数据发送模块内部逻辑框图

数据缓冲模块:对来自数据处理模块发生的数据进行缓冲,进步数据的可靠性和体系的安全性;呈现溢出或许闲暇的时分上报相关信息给数据发送模块操控模块便于OAM。

高速数据串化模块:用时钟分模块供给的高速时钟(为线路时钟速率的3倍或许6倍)对数据进行串化,得到原始数据的3倍或许6倍的串行数据流。

操控模块:接纳来自发送单元数据发送模块的相关信息,通过数据发送模块对内接口模块和OAM模块进行交互,完结OAM模块对本模块的办理。

-

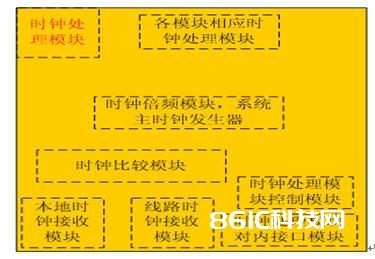

发送单元时钟处理模块

发送单元时钟处理模块完结FPGA内部时钟发生和剖析。模块内部逻辑框图如3.9所示。包含本地时钟接纳模块、线路时钟接纳模块、时钟比较模块、时钟倍频模块、各模块相应时钟处理模块、操控模块和对内接口模块。

图3.9 发送单元时钟处理模块内部逻辑框图

本地时钟接纳模块:接纳来自本地的时钟,本时钟作为OAM 模块、时钟处理器操控模块、并串/串并转化器操控模块的作业基准时钟。以上三个模块的作业时钟由三个模块内部的时钟分模块处理得到。

线路时钟接纳模块:接纳来自时钟处理器的时钟,本时钟经处理后作为数据流方向上相关模块的作业时钟。

时钟倍频模块,体系主时钟发生器:发生体系的主作业时钟,发生重要模块的作业时钟。

操控模块:接纳时钟比较模块和主时钟模块发生器发生的上报信息,对信息进行收拾并对这两个模块进行相关的自动操控;对需求OAM模块办理的信息上签到OAM模块,承受OAM模块的办理。

-

发送单元并串/串并转化器操控模块

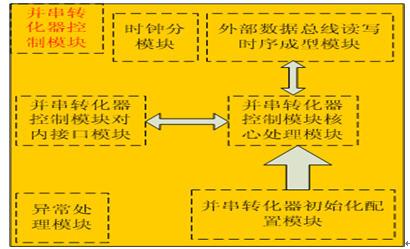

依照串并/并串转化器的办理需求,规划并串/串并转化器的操控办理模块。本模块完结并串、串并转化器的初始化装备,并通过内部接口和OAM模块进行通讯和沟通,由OAM模块进行串并、并串转化器的设置更改。模块内部逻辑框图如图3.10所示。包含操控器中心处理模块外部数据总线读写时序成型模块、时钟分模块、初始化装备模块、对内接口模块 和反常处理模块。

图3.10 发送单元并串/串并转化器操控模块内部逻辑框图

以下是各个分模块的详细介绍。

操控器中心处理模块:完结对并串、串并转化器的中心操控作业,包含对转化器的要害数据的监控、要害设置的承认等作业,是模块的中心子模块。

初始化装备模块:保存串并、并串转化器初始化数据,此数据为默许正常作业的数据,不行更改,假如需求更改则上电装备完结后由OAM模块建议经由中心操控模块对转化器进行操作。

反常处理模块:监测模块内部的反常信息,上报中心处理模块的一起进行必要的操作,确保模块的安稳和安全。

-

发送单元时钟处理器操控模块

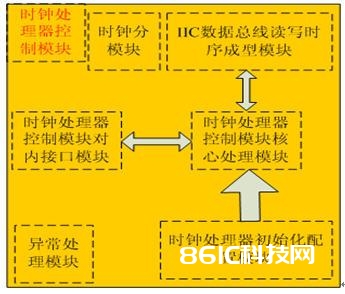

依照时钟处理器的办理需求,规划时钟处理器的操控办理模块,本模块完结时钟处理器初始化装备,并通过内部接口和OAM模块进行通讯和沟通,由OAM模块进行时钟处理器的设置更改。模块内部逻辑框图如图3.11所示。包含操控器中心处理模块、IIC数据总线读写时序成型模块、时钟分模块、初始化装备模块、对内接口模块、反常处理模块。

图3.11 发送单元时钟处理器操控模块内部逻辑框图

操控器中心处理模块:完结对时钟处理器的中心操控作业,包含对时钟处理器的要害数据的监控、要害设置的承认等作业,是模块的中心子模块。

IIC数据总线读写时序成型模块:担任对时钟处理器的读写操作,要求模块彻底满意I%&&&&&%数据总线时序的要求,能精确完结读写操作,并添加相应的防误操作功用,确保读写的正确性。

初始化装备模块:保存时钟处理器初始化数据,此数据为默许正常作业的数据,不行更改,假如需求更改则上电装备完结后由OAM模块建议,经由中心操控模块对时钟处理器进行操作。

-

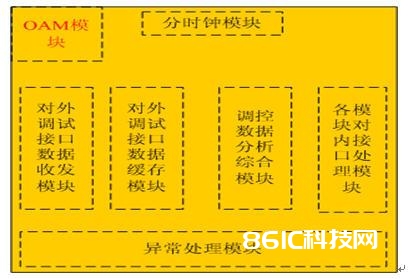

发送单元OAM模块

本模块通过内部接口和发送接纳模块其他体系模块进行通讯和沟通,对其他模块进行操控和办理;一起,本模块通过OAM模块对外接口模块和外部的上层办理操控渠道相连,承受外部上层办理操控渠道的指令,完结相应的操作并上报相关的信息,这部分规划还需求进行沟通承认后才干正常开端规划。模块内部逻辑框图如图3.12。包含对外接口数据收发模块、 对外接口数据缓冲模块、数据剖析归纳模块、对内接口模块、时钟分模块、反常处理模块。

图3.12 发送单元OAM模块内部逻辑框图

以下是各个分模块的详细介绍。

对外接口数据收发模块:完结串口时序的成型,正确完结串口的读写操作,确保读写操作的正确性。。

对外接口数据缓冲模块:缓冲来自串口的信息,在内部处理速度比较慢的情况下仍能确保不丢掉指令。

数据剖析归纳模块:对上层办理渠道的指令进行解析,剖析指令的动作和需求处理的方法,将杂乱指令分化为需求哪几个模块完结什么样的操作,下发给各个实体操作模块。一起对各个实体模块上报的信息进行归纳和办理,编制成契合上层办理渠道需求的回复后回复给上层办理操控渠道。

3.3 接纳部分单元

图3.13 接纳单元电路模块全体框图

接纳部分单元完结六路camera link 总线 (两个 CCD full装备的数据量)的解串作业,先通过波分化复用体系分出每一路camera link 总线的数据,然后再把每一路串化的camera link 数据解串,康复成标准的并行信号。图3.13是接纳单元全体功用框图:

接纳单元包含如下几个模块,如图3.14:

-

接纳单元数据接纳模块:完结正确接纳来自serdes的数据的功用;

-

接纳单元数据处理模块:完结数据的中心处理功用;

-

接纳单元数据发送模块:完结正确将剖析出来的数据发送到Camera link协议转化器的功用;

-

接纳单元串并转化器操控模块:完结对串并转化器的OAM功用;

-

接纳单元时钟处理模块:有用内部的时钟部件完结时钟的相应处理,比方分频、倍频、相位调整等;

-

接纳单元时钟处理器操控模块:完结对时钟处理器的OAM的功用;

-

接纳单元OAM模块:和上层操控办理器的协作,完结发送体系的OAM作业。

图3.14 接纳单元模块区分

下面详细介绍接纳部分单元模块详细功用及完结:

-

接纳单元数据发送模块

接纳单元数据发送模块完结数据的缓冲、对齐处理并发送给camera link 协议转化器的功用。模块内部逻辑框图如图3.15。包含数据缓冲模块、数据对齐模块、输出数据模块、数据发送模块操控模块、数据发送模块对内接口模块、反常处理模块和时钟分模块

图3.15接纳单元数据发送模块内部逻辑框图

数据缓冲模块:对发送单元数据处理模块发生的数据进行缓冲,进步数据的可靠性和体系的安全性;呈现溢出或许闲暇的时分上报相关信息给数据发送模块操控模块便于OAM。

数据对齐模块:对数据进行对齐操作,并进行相关的处理,确保发送出去的数据满意camera link 的标准要求。

输出数据模块:进行时序调整,将数据发送到camera link 协议转化器。

操控模块:接纳来自接纳单元数据发送模块的相关信息,通过数据发送模块对内接口模块和OAM模块进行交互,完结OAM模块对本模块的办理。

对内接口模块:完结数据发送模块操控模块和接纳单元OAM模块之间的通讯和数据沟通。

反常处理模块:供给不行猜测的反常处理,比方复位等,以进步体系的可靠性和安稳性。

时钟分模块:供给本模块需求的时钟。

-

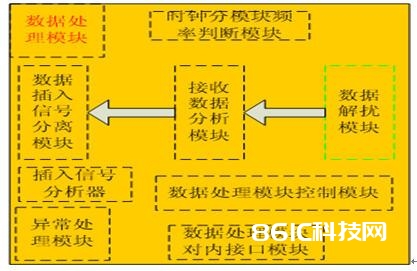

接纳单元数据处理模块

接纳单元数据处理模块完结中心的数据接纳的功用。模块内部逻辑框图如图3.16所示。包含数据解扰模块、数据剖析模块、数据刺进信号别离模块、刺进信号剖析器、数据处理模块操控模块、数据处理模块对内接口模块、时钟分模块、反常处理模块。

图3.16接纳单元数据处理模块内部逻辑框图

以下是各个分模块的详细介绍。

数据解扰模块:该模块首要完结解扰进程,确保正确提取数据。

数据剖析模块:完结30bit的帧结构的定帧操作,并正确确认出28bit数据信号和相应的定帧信号,并断定数据是否通过double处理。作业状况可以由数据处理模块操控模块进行相关的设置和监测。

数据刺进信号别离模块:正确别离出数据和刺进信号。依据是否对数据进行double处理断定camera link 总线的时钟频率,处理后的数据为真实的接纳数据。

刺进信号剖析器:剖析对端刺进的数据,提取相关的信息,并上签到操控模块。

-

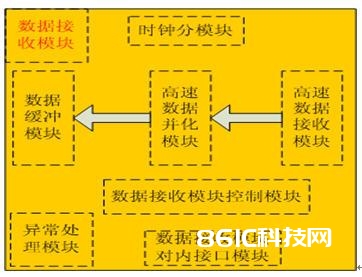

接纳单元数据接纳模块

接纳模块数据接纳模块完结串行数据高速接纳、高速串化数据的并化处理、数据缓冲的功用。模块内部逻辑框图如图3.17所示。包含高速数据接纳模块、高速数据并化模块、数据缓冲模块、数据接纳模块操控模块、数据接纳模块对内接口模块、反常处理模块和时钟分模块。

图3.17接纳单元数据接纳模块内部逻辑框图

以下是各个分模块的详细介绍。

高速数据接纳模块:以和Serdes 相匹配的方法接纳来自serdes的高速数据。

高速数据并化模块:完结高速数据的串并转化功用。

数据缓冲模块:对接纳数据进行缓冲,进步数据的可靠性和体系的安全性。呈现溢出或许闲暇的时分上报相关信息给数据接纳模块操控模块便于OAM。

-

接纳单元时钟处理模块

接纳单元时钟处理模块和发送单元选用相同的计划。可拜见发送单元。

-

接纳单元并串/串并转化器操控模块

接纳单元并串/串并转化器操控模块和发送单元选用相同的计划。可拜见发送单元。

-

接纳单元时钟处理器操控模块

接纳单元时钟处理器操控模块和发送单元选用相同的计划。可拜见发送单元。

-

接纳单元OAM模块

接纳单元OAM模块和发送单元选用相同的计划。可拜见发送单元。

3.4 发送、接纳单元并串/串并转化器模块

依据体系的规划需求,可以用一款通用串行器及解串器组成高速并串、串并模块。串行/解串器芯片组数据串行速度最高速度应高于Camera link的最高的2.38Gbps速率,以确保CCD在最高速率下可以运用;串行/解串器芯片组数据串行速度下限应低于Camera link的最低的560Mbps速率,以确保CCD在最低速率下可以运用。而且解串器不需求本地的时钟,彻底在串行码流中提取时钟。一般芯片在满意最高速度要求的情况下,在满意最低速率需求方面存在问题,无法满意camera link 的最低560Mbps的要求,则需求对速率较低的camera link 数据进行倍速调整,以到达串化/解串芯片组可以支撑的速率,这也是该体系规划中规划难点之一。

3.5 OAM接口模块

OAM接口模块选用422/232兼容的接口模块,规划相对简略。OAM模块详细的功用规划已经在之前中心模块中有详细描述,这儿不赘述。

四、发送板及接纳板实物图

图4.1 发送板实物图

图4.2 接纳板实物图