过采样技能是数字信号处理者用来进步模数转化器(ADC)功用常常运用的办法之一,它通过减小量化噪声,进步ADC的信噪比,然后进步ADC的有用分辩率[1]。过采样技能不光没有添加额定的模仿电路,而且因为进步了有用分辩率还能简化模仿电路,而且简单易行,因而被数字信号处理实践者广泛运用于测控范畴[2-6]。

过采样技能的一个关键环节是采样后的低通滤波器(LPF, Low Pass Filter),没有这个滤波器,过采样发生不了任何作用[7]。可是,许多运用中,需求丈量多种信号,数据收集部分有必要具有自适应特性,即依据输入信号的频带能自主挑选下抽取率,过采样后低通滤波器的特性也应随之改动。因而,有必要规划一款参数可变的低通滤波器来满意这种需求。

过采样技能中的低通滤波器

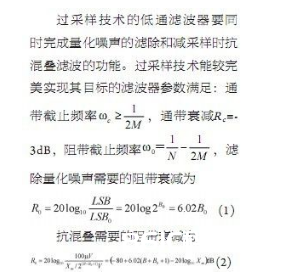

过采样技能的低通滤波器要一起完结量化噪声的滤除和减采样时抗混叠滤波的功用。过采样技能能较完美完结其方针的滤波器参数满意:通带截止频率,通带衰减Rc=-3dB,阻带截止频率,滤除量化噪声需求的阻带衰减为

其间,M为过采样率,N为下抽取率,B为ADC原有的分辩率,B0为进步的分辩率,N=4B0,而且一般有 。而滤波器的类型为FIR滤波器,其阶次与下抽取率成正比。

可变参数低通滤波器的规划

由2节可知,过采样中的滤波器特性由ADC本身的分辩率和下抽取率决议。下抽取率改动,滤波器参数会发生改动,滤波器则有必要从头规划。从FIR滤波器的规划流程[8]来看,截止频率改动后,滤波器系数会随之改动。假如取得截止频率后再核算滤波器系数,会带来很多运算量,因为每核算一组滤波器系数都要进行一次IFFT(Inverse Fourier Transform)。一般的做法是在PC机上核算出系数后,做成查找表。因为下抽取率改动,这样的表会有很多张,会耗费很多存储空间。而本末节选用的办法,避免了这种状况,选取一组适宜的滤波器系数,便可完结多种下抽取率的滤波。

滤波器系数决议滤波器特性,理论上讲,只用一组滤波器系数是不能完结可变参数滤波器的。由2节可知,下抽取率N与滤波器截止频率成反比,与阻带衰减成正比,与滤波器长度成正比。假定下抽取率为N0时滤波器系数h(n),n=0,1,2…L-1,咱们怎样通过h(n)这组基准系数来取得N不等于N0时的滤波器系数呢?

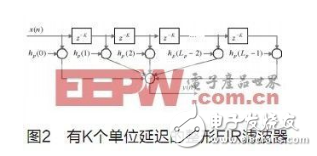

当N插值FIR滤波器是在L抽头、非递归线性FIR滤波器的功用基础上,将L抽头的FIR滤波器各个抽头之间的一个单推迟,用K个单位推迟替代而规划构成的,K为扩展因子,是一个整数,如图2所示。本来的FIR滤波器称为原型滤波器,具有扩展推迟的滤波器称为整形子滤波器。

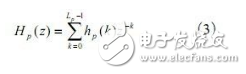

原型FIR滤波器在z域的传递函数为:

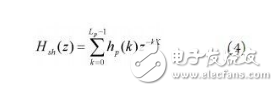

式(3)中,Lp为hp的长度。则整形子滤波器传递函数为:

其扩展冲激呼应长度为 ,反映到时域上,整形子滤波器系数为:

,反映到时域上,整形子滤波器系数为:

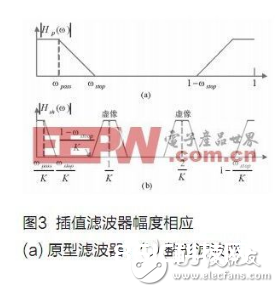

图3给出了K=3个单位推迟在频域的影响。时域滤波器冲激呼应扩展K倍,导致频域 起伏呼应紧缩K倍,如图3(b)。图中那些以1/K整数倍为中心、重复呈现的

起伏呼应紧缩K倍,如图3(b)。图中那些以1/K整数倍为中心、重复呈现的 的通带称为虚像。只需将这些虚像滤除,就能取得衰减特性不变,截止频率为原滤波器截止频率1/K的滤波器,刚好契合过采样后低通滤波器截止频率与下抽取率成反比的特性,因而可用于过采样中可变参数滤波器的规划。此处,滤除虚像的滤波器称为约束虚像滤波器。

的通带称为虚像。只需将这些虚像滤除,就能取得衰减特性不变,截止频率为原滤波器截止频率1/K的滤波器,刚好契合过采样后低通滤波器截止频率与下抽取率成反比的特性,因而可用于过采样中可变参数滤波器的规划。此处,滤除虚像的滤波器称为约束虚像滤波器。

插值滤波器其实是整形子滤波器和约束虚像滤波器的级联。整形子滤波器很好完结,只需在原型滤波器系数的基础上按要求刺进零值即可,下面首要看约束虚像滤波器的规划。当下抽取率大于必定值时,低通滤波器为窄带滤波器,则整形滤波器的虚像也为一窄带。均匀滤波器的起伏呼应在1/L的整倍数处为一窄带陷波器,能够滤除整形滤波器发生的虚像。虚像呈现在1/K的整倍数处,因而,只需使得作为约束虚像滤波器的均匀滤波器的长度满意, ,便能够滤除虚像。

,便能够滤除虚像。

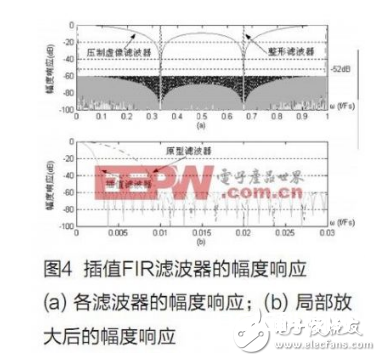

图4为 时,原型滤波器、整形滤波器、约束虚像滤波器和终究取得的插值滤波器的起伏呼应,原型滤波器为FIR切比雪夫滤波器。从图4(a)能够看出,虚像呈现的方位与均匀滤波器的零点方位对齐,然后按捺了虚像。因为太小,均匀滤波器的旁瓣宽度较大,陷波带大于虚像带宽,导致虚像的按捺没有到达滤波器要求的阻带衰减。可是,虚像所在频率与过采样频率适当,此处呈现的噪声仅为量化噪声,此处衰减特性只需将其按捺到ADC分辩率进步后的量化噪声水平,即满意过采样的要求。例如:ADC分辩率通过采样后进步6位,其要求的衰减特性为-36.1dB,而图4(a)插值滤波器虚像处的衰减为52dB,足以满意大部分规划的要求。

时,原型滤波器、整形滤波器、约束虚像滤波器和终究取得的插值滤波器的起伏呼应,原型滤波器为FIR切比雪夫滤波器。从图4(a)能够看出,虚像呈现的方位与均匀滤波器的零点方位对齐,然后按捺了虚像。因为太小,均匀滤波器的旁瓣宽度较大,陷波带大于虚像带宽,导致虚像的按捺没有到达滤波器要求的阻带衰减。可是,虚像所在频率与过采样频率适当,此处呈现的噪声仅为量化噪声,此处衰减特性只需将其按捺到ADC分辩率进步后的量化噪声水平,即满意过采样的要求。例如:ADC分辩率通过采样后进步6位,其要求的衰减特性为-36.1dB,而图4(a)插值滤波器虚像处的衰减为52dB,足以满意大部分规划的要求。

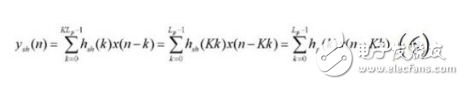

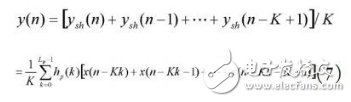

插值滤波器在过采样中的完结的流程为:在原型滤波器进行K倍内插后,再做K点的均匀滤波即可。看上去需求两步才干完结低通滤波,实践上,因为整形和均匀滤波的特性,咱们能够一步完结滤波。由式(3)可知,整形子滤波器的输出为:

为下抽取及核算便利,将整形滤波器的长度从 ,改为KLp 。因为FIR滤波器系数的不敏理性,这样做并不会影响滤波器特性。则插值滤波器的输出为:

,改为KLp 。因为FIR滤波器系数的不敏理性,这样做并不会影响滤波器特性。则插值滤波器的输出为:

由式(4-9)可知,插值滤波器输出是将K点值均匀后,再与原型滤波器系数加权均匀的成果。能够看出,完结办法很简单。

过采样技能在FGPA的完结

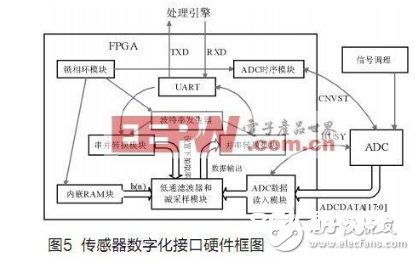

一些通用的数据收集模块需求完结多种信号的丈量,重视模块的通用性,因而,扩大、滤波等信号预处理电路这样的特性事物是不被答应存在的。将过采样技能运用于通用模块,省掉信号预处理电路,依据信号特色,选取适宜的过采样率和下抽取率,平衡终究采样率和分辩率,来获取要求的丈量精度。依据通用模块的要求,规划了图5所示结构来完结通用模块的过采样技能。

由图5可知,FPGA完结了以下功用:发生ADC时序,操控ADC的采样频率;以ADC转化完毕标志位为触发信号,读取ADC的转化数据;为滤除ADC输出信号的量化噪声和减小数据量,完结低通滤波和减采样模块;装备一块ROM区,用于存储滤波器系数,用于滤波器的完结;为与外部处理引擎进行通讯,完结UART接口协议;为使个模块和谐作业,选用锁相环发生不同频率的时钟。

而模块的作业流程为:处理引擎将待测信号的频率通过UART传给低通滤波和减采样模块,该模块依据该频率设置滤波器参数和减采样的下抽取率;ADC时序模块发生CNVST,发动ADC进行采样,BUSY信号触发数据读取模块将数据读入;低通滤波器和减采样模块依据设置好的参数和下抽取率对读入的数据进行处理,处理完毕后,再将数据通过UART传到处理引擎做后续处理。

模块中的ADC选用的是ADI公司的AD7674,18位、800KSPS逐次迫临型模数转化器,具有较高的数据通过率。支撑差分输入形式,其内部采样坚持电路的负载可调,5V单电源供电。器材内部还集成了转化时钟、基准缓冲器及过错校准电路,并具有功用强大的串口和并口,与3V和5V电平兼容。而FPGA则选用的是Altera CycloneⅡ-EP2C8Q208C8,包含5个部分:可编程输入/输出单元、根本可编程逻辑单元、嵌入式块RAM、丰厚的布线资源和底层嵌入功用单元。

依据AD7674和EP2C8,该模块规划取得的相关参数为:

(1) 下抽取率 ,过采样率

,过采样率 ,因为ADC的最高采样频率为800KSPS,则该模块可用于0Hz -32kHz信号的丈量;

,因为ADC的最高采样频率为800KSPS,则该模块可用于0Hz -32kHz信号的丈量;

(2) ADC的本身分辩率为18位,过采样后到达的最大分辩率为25位;

(3) ADC基准电压为4.096V,最高分辩率时可分辩的信号巨细为:

(4) 为使ADC到达25位分辩率,除满意下抽取率N=47外,还有必要确保低通滤波器的阻带衰减契合过采样的要求。由式(1)和(2)可知, 阻带衰减R0=64.3dB。运用切比雪夫最佳迫临法取得滤波器系数,通过核算及考虑到规划余量,得到滤波器长度L=4N,N=47时,实践阻带衰减为R0=75dB;使用MATLAB软件中的函数CHEBWIN(L,R0)取得滤波器系数;将滤波器系数量化成8位,并进行16倍下抽取,抽取后的值对应为N=45 时的滤波器系数。将其存入FPGA的ROM区,以此为基准得到其他下抽取率的滤波器系数。

(5) 完结该模块耗费的FPGA资源为:7275个LE(88%),65544个memory bits(40%),24个9位乘法器(67%),27个I/O口(20%)1个PLL(50%)。

试验成果和剖析

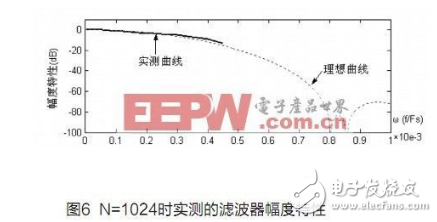

为调查模块规划的正确性,对其进行了测验。首要分为两个部分。第一部分为低通滤波器的测验。首先以N=1024 为例,验证实践滤波器的起伏特性是否与规划的共同,然后验证可变参数低通滤波器规划的正确性。第二部分则以心电信号为例,验证模块分辩率与过采样率的联系。

图6为N=1024时,MATLAB规划的滤波器起伏特性和实测的滤波器起伏特性的比对。测验办法为:ADC的采样率为800kHz,下抽取率为1024,终究采样率为 ;给体系参加3V不同频率的正弦波,频率规模为5Hz-360Hz;取得的数据传到PC上,用MATLAB核算各组数据的FFT取得起伏值;假定5Hz的正弦波通过体系后起伏不发生衰减,以此为基准核算各频率点的衰减状况。由图6可知,实测的起伏特性与规划的根本共同。不足之处是,受采样率的约束,被测信号频率不能大于采样率的一半,咱们只能得到部分采样点的衰减状况。

图7是可变参数滤波器在不同下抽取率时的起伏特性。为验证改动参数时滤波器是否正常作业,给体系输入信号为2V、20Hz正弦波和0.95V、90Hz正弦波的加性信号,ADC别离以采样率12.5kHz、50kHz、200kHz、800kHz对加性信号采样,下抽取率依次为64、256、1024、4096,则四组数据的终究采样率均为195Hz。以20Hz正弦波为基准,验证90Hz正弦波的衰减状况。图7中每条曲线上的黑点对应的是90Hz的衰减特性,别离为:15.345dB、15.504 dB、15.54 dB、14.958 dB。图8是信号通过体系后的频谱剖析。由图8可知,90Hz的正弦波显着得到了按捺,其衰减别离为:16.896 dB、14.408 dB、17.345 dB、14.804 dB,实测的数据与规划的根本共同,阐明各参数下的滤波器能正常作业。别的,图8中三个小的尖峰,别离为50Hz搅扰和20Hz的谐波。

图9是体系测得的试验室某同学的心电波形。由图9可知,跟着下抽取率的增大,心电信号的细节越来越清楚,即分辩率越来越高。因而,随者下抽取率的增大,体系的分辩率是添加的。

综上所述,依据过采样技能的通用数据收集模块能够依据被测信号的不同,改动本身的参数,到达丈量要求,一起,也完结了可变参数低通滤波器的硬件完结。

结语

为减小通用数据收集模块的体积和本钱,将过采样技能运用于模块的ADC中。因为通用模块丈量多种信号,为到达过采样对低通滤波器的要求,规划了可变参数低通滤波器。该滤波器简单易行,而且核算效率高,在本文规划的通用模块中,每取得一个采样点,最多只需进行4次18bits×8bits的乘法运算。

此外,本文从硬件上完结了该模块的规划,并对模块进行了测验,终究以心电为例,验证了参数的可变性。