1 导言

相位计是用于丈量两个具有相同改变规则的信号之间相位差的仪器。两个相同频率信号之间的相位差有多种丈量办法。常用的相位-时刻转化办法是传统数字式相位差计选用的一种办法,此种办法通用性和灵敏性均较差,依据CPLD的虚拟相位计由数据收集、单片机及CPLD(可编程逻辑器材)等组成。

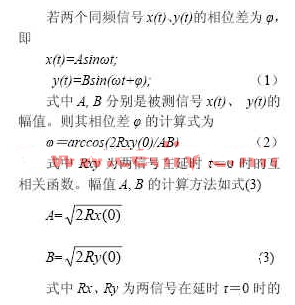

2依据相关原理的虚拟相位差丈量法

3虚拟相位计结构

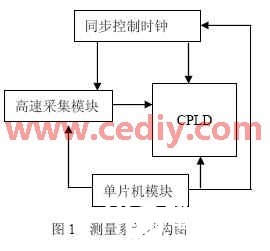

虚拟相位计主要由高速数据收集模块、单片机模块、同步时钟操控模块和CPLD组成。以高性能、高集成度、低功耗系列CPLD作为中心核算部件,担任进行自相关和互相关剖析,同步操控时钟担任采样及相关剖析的同步核算,运用CPLD高档成集成、高速、高可靠性的特色,满意体系实时、快速丈量要求。

体系由单片机发动数据收集和CPLD核算。高速收集模块一起对两个同频信号 x(t)、 y(t)采样,将采得时刻序列x(n)和y(n)送往CPLD, 同步时钟一起操控CPLD进行相关剖析。采样及相关剖析完毕后,其核算结果由单片机取出进行反三角函数核算,然后得出相位差。

4 CPLD结构规划

本体系中的CPLD是选用FLEX10K系列EPF10K100TC144-3。该芯片具有高密度、低功耗、高速度和灵敏的互联办法,支撑多电压接口,多种装备的特色。

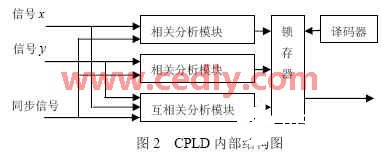

结构剖析

依据体系要求,芯片内部主要由核算模块组成。分为信号1自相关剖析模块、信号2自相关剖析模块、和互相关剖析模块。结构如图2所示。本规划运用MAXPLUSΠ软件,依据本体系的逻辑结构,运用图形化输入办法进行程序规划。

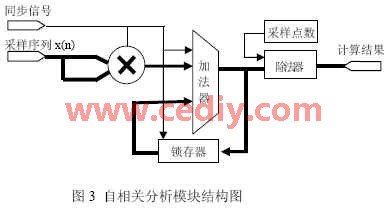

自相关剖析模块

相关剖析模块主要由乘法器、加法器和除法器组成。同步信号操控平方、相加和相除运算的同步进行,采样点数可由单片机进行赋值。模块结构如图3所示。

在图形化编程中,锁存器、乘法器、加法器和除法器均为LPM(参数化模块库) 中元件。在编程中可经过设置参数来完成器材运算速度和数据线宽度的装备。

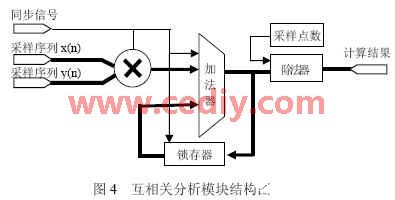

互相关剖析模块

互相关剖析模块结构如图4所示。

5定论

本文介绍的依据CPLD的虚拟相位丈量体系选用了现在比较先进的可编程器件技能和虚拟仪器技能,经过CPLD的相关剖析和采样同步进行,可大大削减单片机的核算作业,并对体系存储资源的需求减到很小。可是,因为CPLD核算速度的约束,尽管把器材设置在高速运转并流水规划到最佳,此体系对高频信号的丈量仍较困难。跟着CPLD技能的开展,对高频信号的丈量将有所改善。

责任编辑:gt