SoC FPGA为一个整合FPGA架构、硬式中心CPU子体系以及其他硬式中心IP的半导体元件,可完成低延时频宽互联,并前进IP重用性;预估此类型元件在往后10年中将会得到广泛运用,为体系规划人员供给更多的挑选。

整整合了现场可编程闸阵列(FPGA)架构、硬式中心中央处理器(CPU)子体系以及其他硬式中心矽智财(IP)的半导体元件–SoC FPGA,现已开展到了一个“要害点”,它在往后10年中会得到广泛运用,为体系规划人员供给更多的挑选。在各种技能、商业和商场要素相结合下,推进了这一个要害点的呈现,Altera、赛普拉斯(Cypress)、英特尔(Intel)和赛灵思(Xilinx)等供货商,都相继发布或开端出售SoC FPGA元件

本文章介绍新呈现的SoC FPGA,背面的推进要素,以及履行管理人员和体系规划人员在挑选这些元件时的考虑要素。

业界整合FPGA和CPU体系在第一个10年开展中既有成功也有失利。开端的SoC FPGA在商业上并不是很成功,而FPGA中的软式中心CPU得到了广泛应,这证明商场对FPGA和CPU技能整合有根本的需求。各种新的要素改变了业界环境,导致要害点的呈现,SoC FPGA将在商场上取得十分广泛的运用。

从FPGA朝向SoC FPGA开展,首要有几个要害的推进要素,包含FPGA开端选用如28奈米(nm)之类的先进半导体制程技能,藉由摩尔定律完成更高本钱效益;一起,CPU架构的增强,并过渡到平行和多中心处理,以及嵌入式体系选用FPGA的比率愈来愈高,亦有火上加油之效。

运算功率效益大增

由于运算的开展趋势是朝向平行处理技能,处理器亦从高本钱的单中心处理,一向开展到如今的多中心。为了在前进运算功用的一起,也能下降功率耗费,促进一些厂商开端选用FPGA逻辑做为CPU的硬体加快器,带动SoC FPGA开展风潮。

一个SoC FPGA体系可前进功率效益,并完成灵敏的软体画分。SoC FPGA可援助数百路材料信号衔接不同的功用区,完成100Gbit/s频宽,乃至更大的频宽,其延时在奈秒级,功用和延时体现都比独立元件好,而且其整合渠道亦可前进记忆体存取功用。

SoC FPGA功用前进以及记忆体存取功用完成功用更强的加快器,可以满意林林总总的运算要求。由于硬体加快器在功率效益上要比CPU还高1,000多倍,因而,与简略的多中心平行办法比较,选用SoC FPGA进行规划对开发人员而言,是完成高功率效益运算较好的办法。

顶级制程技能加持 SoC FPGA兼具低功耗与高效能

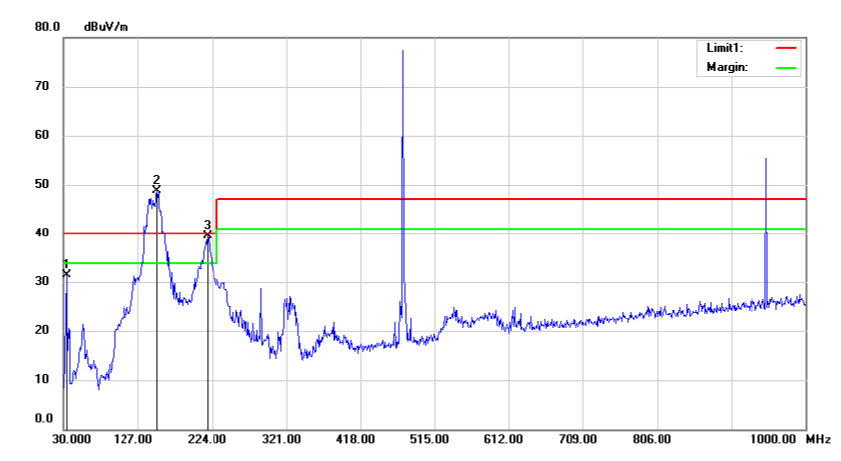

如图1所示,在2000年时,最新的FPGA选用了130奈米制程技能进行开发,而其时的CPU选用的是90奈米制程技能。由于商场上已有更高阶的CPU,因而,第一代SoC FPGA的推出显得有些落后。但是,当今最顶级FPGA已选用28奈米制程技能,相对而言只要少量商用CPU或许特定运用规范产品(ASSP)运用28奈米制程技能。FPGA的制程技能在整合元件的商场优势已显着增强,而FPGA供货商也倾向于在SoC FPGA方面许多投入产品研制,这是由于该产品可让客户不需要在CPU功用与功耗上做出退让。

图1 FPGA制程技能演进进程

FPGA于嵌入式体系运用日渐添加

曩昔关于大部分嵌入式体系运用,FPGA往往是客户觉得较为贵重的元件,也因而与相应的杂乱型可编程逻辑元件(CPLD)或许可程式化阵列逻辑(PAL)比较,其运用相对较少。但是,在曩昔10年中,选用静态随机存取记忆体(SRAM)架构的FPGA在下降本钱上现已逾越了互补式金属氧化物半导体(CMOS),如今,已有挨近50%的嵌入式体系选用了FPGA。而SoC FPGA最明显的优势是本钱可比独立元件低许多,晶片供货商将会有很大的商场时机取得出资报答。

ASSP本钱渐高 SoC FPGA有机可趁

摩尔定律在未来将显得越来越“贵重”。开发高阶CMOS的制作设备本钱大约在10亿~60亿美元,其间还需要4,000万美元的本钱来开发新的半导体元件,因而,在典型的赢利模型中,半导体元件应可以取得1亿美元的毛利,而其间20%的收益须花在研制上。而当典型的毛利是50%时,企业至少要占有2亿美元的商场份额。除消费性电子、举动电话和个人电脑(PC)外,事实上,很少有可以到达这一种规划的运用商场,因而,单一意图或许固定功用的元件很难取得出资报答。在往后的制程技能中,高阶半导体的本钱将会越来越高,这一种本钱结构使得开发固定功用半导体元件很难取得较好的出资报答,这代表着在可程式规划逻辑技能上的投入可望越来越多,而专用ASSP和CPU等固定功用元件的投入则会越来越少。SoC FPGA有潜力运用于许多商场范畴,并将会取得更多的投入。

扩展运用商场 FPGA商选用CPU架构蔚为潮流

嵌入式处理这一个术语其实涵盖了多种运用,从对本钱十分灵敏的4位元处理器到十分杂乱的多中心64位元处理器。这种广泛的运用一向援助各种类型的处理器、作业体系和软体供货商。与10年前比较,这种广泛性在2011年体现出很大的不同,关于其规划和多样性而言,嵌入式商场全体生长速度不光快,且处理器功用的开展亦日趋前进;例如16位元微控制器逐步被32位元CPU代替。一起,四种运用最广泛的架构进一步增强了对32位元CPU系列的援助,这些架构包含安谋世界(ARM)、MIPS、PowerPC和x86。之所以对其进行增强动作,首要是由于软体特性和功用重用。而选用了这些CPU架构之一的SoC FPGA可以占有更大的商场,因而,FPGA供货商更乐意在这类半导体上扩展出资。

渠道效应加快SoC FPGA规划趋势成形

出产厂商、运用者和辅佐援助体系在产品上彼此之间会有影响时,就会呈现网路效应,或许称为渠道效应。渠道效应的根本原理是某一种产品或许规范的运用越多,它在运用者根底和辅佐援助体系中的价值就越高。成果,运用者根底和辅佐援助体系就会在这种技能上加大投入,从而招引更多的运用,发生一种自我增强的良性循环。了解的比如包含PC、视讯记载格局和交际网站等。

一般来说,有或许发生自我增强循环的产品将会在这种循环中不断开展,这是由于参加到新产品中的一切成员都会取得较高的出资报答。渠道效应一旦开端发动后,就会招引各家厂商争相投入,而SoC FPGA商场则很快就会转向这一个规范。

跟着SoC FPGA的不断开展,用户将十分乐意从头运用他们在多种体系中运用过的FPGA IP和规划软体。例如,CPU辅佐援助体系中的成员乐意尽或许削减学习FPGA开发东西,而CPU供货商也期望削减FPGA开发东西的数量。终究,援助多家供货商和CPU架构的SoC FPGA渠道很有或许触发这种渠道效应,协助这些运用者和辅佐援助体系成员取得很大的优势。

以FPGA业者Altera为例,其在嵌入式体系进步行了多年的立异投入后,已发动了“嵌入式方案”,意图是树立一个可让多家供货商选用同一种FPGA规划流程办法,并可运用多CPU架构的SoC FPGA渠道。

FPGA规划流程办法可以作为多种SoC FPGA的根底,以及运用软式中心CPU和其他软式中心IP的SoC解决方案。例如FPGA厂商可取得ARM(硬式中心)、MIPS(软式中心)和Nios II(软式中心)CPU或许由英特尔供给的Atom E6X5C可装备处理器。这种整合办法可在一种FPGA架构和规划流程中,一致三种首要的CPU架构,以及最盛行的、选用FPGA架构的软式中心CPU。

FPGA规划流程整合办法旨在鼓励辅佐援助体系从首要处理器架构,转向投入单一FPGA渠道和东西流程,从而带来丰厚的东西、运用软体、作业体系软体和专业知识援助。随数百家全球辅佐援助体系成员在CPU架构上的投入,此一FPGA渠道及其越来越多的东西、软体和IP运用亦日趋广泛,对体系规划人员也越来越重要,证明其价值定位将促进更多运用,从而推进了良性渠道的工业生态。

前进SoC FPGA规划功率 体系整合东西人物吃重

这一个多供货商渠道的组成要害,是可对FPGA逻辑进行程式规划的Quartus II软体。Quartus II软体包含Qsys体系整合东西,选用了Altera的第二代交流架构技能,用于加快软式中心IP的开发、重用和整合。选用运用者图形介面(GUI)架构的Quartus II软体有免费的网路版和彻底授权的版别,其可供给包含体系规划、时序收敛、体系验证,以及协力厂商电子主动化规划(EDA)东西援助,从而满意了效能和功用上的需求。

除Altera传统的Avalon记忆体映射(Avalon-MM)介面和材料通路汇流排介面规范,Qsys还援助ARM AXI规范,可以选用主动的混合匹配办法来整合选用Avalon架构的IP和选用AXI架构的IP。Qsys亦援助使用直观快速的规划经历,在通用渠道上可便利进行规划或许体系内验证,从而完成选用ARM架构和Intel的SoC FPGA,以及完成选用MIPS和Nios II软式中心CPU的SoC。

客制化28奈米系列元件 强化产品竞争力

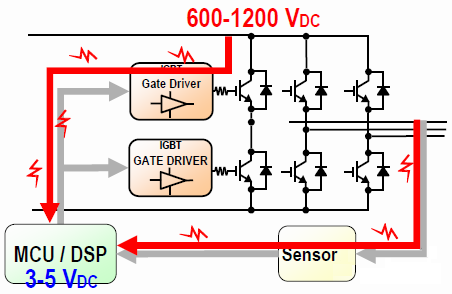

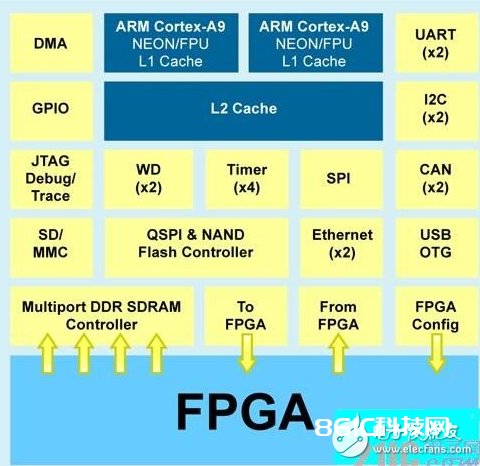

Altera的28奈米FPGA系列元件可针对用户各种规划需求进行客制化,并可为各种终端运用需求供给恰当的FPGA架构和制程技能,如高效能的Stratix V元件、低本钱的Cyclone V元件以及在功用和本钱上到达均衡的中阶Arria V元件。全系列SoC FPGA皆获益于28奈米制程所带来的优势。此外,如图2所示,最新的SoC FPGA亦将含有选用ARM Cortex-A9架构中心的高阶处理器模块。

图2 Altera SoC FPGA架构

Altera SoC FPGA架构在ARM Cortex-A9子体系中,将含有多种硬式中心IP,以及高功用多埠记忆体控制器,以前进记忆体频宽。FPGA和CPU子体系之间的宽频低延时互联,将援助高功用运用和高功率的FPGA硬体加快。高阶内部交流架构将援助高功率的材料传输量,以及高效能在体系调查和除错。Qsys、Quartus II软体以及ARM社群软体东西相结合后,这一个元件将是一种性价比十分高的体系规划挑选,其可使用规范东西流程前进效能,援助新开发和验证。

在本钱要求日趋苛刻、制程技能老练和商场需求添加的要素推进下,SoC FPGA年代现已降临。现在已有些FPGA供货商发布了SoC FPGA相关产品,亦尚有许多厂商正在加紧脚步研制中。体系规画人员在评价体系解决方案时,应该仔细考虑渠道效应、IP重用以及FPGA制程技能优势,以挑选最佳的解决方案。

此外,Altera与首要的CPU供货商ARM、Intel和MIPS协作,为SoC FPGA元件和软式中心CPU解决方案供给公共FPGA渠道。这种协作关系可以完成业界运用最广泛的CPU架构及其辅佐援助体系,承继相同的高阶FPGA规划流程,从而在这一个渠道上增强了IP重用,前进灵敏性。这种整合办法将会完成了渠道效应,而且促进SoC FPGA以及其辅佐援助体系的添加和开展。