基于可编程逻辑器件和IPX2805实现SPI4.2接口电路的设计-SPI-4.2(System Packet Interface)是 OIF(Optical Internetworking Forum)定义的局部高速总线标准,用于 PHY层芯片到链路层芯片的 10Gbps信号传输。主要应用有 OC-192 ATM、Packet over SONET/SDH(POS)、10Gbps以太网等。

基于复杂可编程逻辑器件的VME总线接口逻辑系统的设计-机载计算机的几何结构一般采用高强度机箱和底板来连接各功能模块。底板总线类型大部分采用VME总线规范。VME总线是1981年Motorola等公司为欧洲板(Euroboard)设计的总线,是欧洲通用模块(VME-Versa Module Europe)的首字母缩写。经过二十多年的演变发展,已经成为美国国家标准。它以高性能、并行性、实时性和高可靠性四大特点赢得机载计算机青睐,模块结构具有良好的抗震性,抗冲击能力。本文结合我们的实际工作,重点介绍VME总线接口逻辑的工程实践方法。

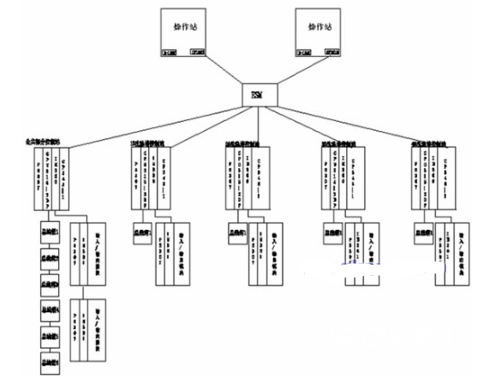

采用西门子S7-300系列PLC和总线技术实现高炉煤气洗涤控制系统设计-如果采用常规PLC集中控制方式,将现场信号通过电缆连接到集中控制室内的PLC上,由于工艺线路长、现场控制点分布范围广,需要敷设大量的电缆及桥架,且现场环境恶劣、其施工难度非常大。鉴于此,采用了PROFIBUS-DP现场总线技术,根据工艺划分,系统共设了五个主站、十个总线箱、两个操作员站。采用西门子的S7-300系列PLC,主站采用CPU315-2DP,其带有一个DP通讯口和一个MPI口。各总线箱采用通用性较好的ET200B和ET200eco现场模块,用于现场数据的采集和控制,并借助Profibus(工业现场总线),方便控制网络系统的建立。

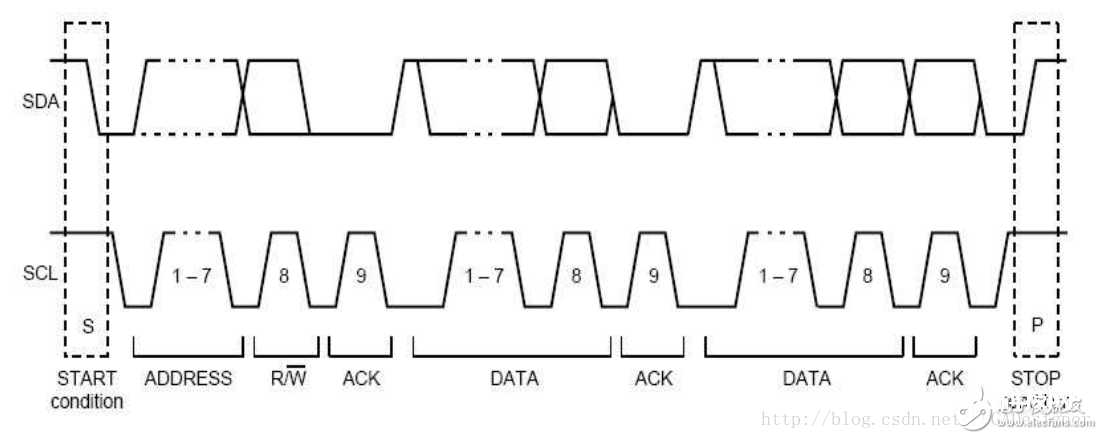

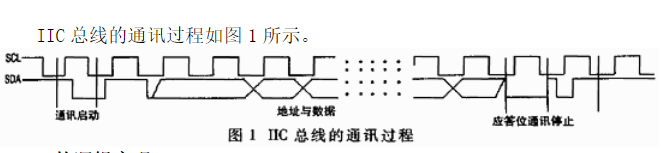

FPGA基础知识之IIC协议读写解析-很多数字传感器、数字控制的芯片(DDS、串行ADC、串行DAC)都是通过IIC总线来和控制器通信的。不过IIC协议仍然是一种慢速的通信方式,标准IIC速率为100kbit/s,快速模式速率为400kbit/s。本文致力于讲述如何用计数器控制和分频时钟控制两种方式完成IIC的读写操作。 IIC协议 IIC协议是一种多机通讯,由SDA数据线和SCL时钟线构成串行总线,所有的IIC设备都可以挂载到总线上,但每个设备都有唯一的设备读地址和设备写地址。在使用IIC作为数字接口的芯片

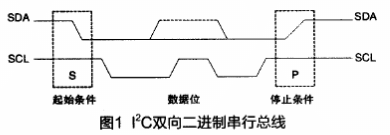

Core I2C的原理及采用FPGA技术实现I2C IP核的设计-I2C(Inter Integrated Circuit)双向二线制串行总线,是由飞利浦公司制定的。I2C总线是一个多主机的总线,使用串行数据线(SDA)和串行时钟线(SCL)在总线上传递信息。每个器件都有一个唯一的识别地址,而且都可以作为一个发送器或接收器。当连接在I2C总线上的多个主机器件同时传输数据时,通过仲裁来避免冲突。SDA和SCL都是双向线路,通过一个电流源或上拉电阻连接到电源。器件输出级必须是漏极开路或集电极开路,当总线空闲时,两条线路处于高电平,执行线与的功能。

采用VHDL-93语言和可编程芯片实现IIC总线接口的芯片功能设计-IIC总线是PHILIPS公司开发的一种简单、双向、二线制、同步串行总线。它只需两根线(串行时钟线和串行数据线)即可在连接于总线上的器件之间传送信息。该总线是高性能串行总线,具备多主机系统所需要的裁决和高低速设备同步等功能,应用极为广泛。

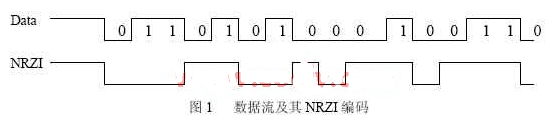

使用CPLD器件和VHDL语言实现USB收发模块的硬件功能设计-当前,高密度可编程逻辑器件CPLD,由于具有巨大的灵活性而广泛应用于状态机、同步、译码、解码、计数、总线接口、串并转换等很多方面,而且在信号处理领域的应用也活跃起来。通用串行总线(USB,Universal Serial Bus)接口既是一种快速、双向、廉价、可以进行热插拔的串行接口技术,也是一种体系完备的通信协议,已逐渐成为计算机的主流接口。USB接口的收发模块用于进行数据编码和与外部相连。本文主要介绍使用CPLD实现通用串行总线(USB)接口收发模块。

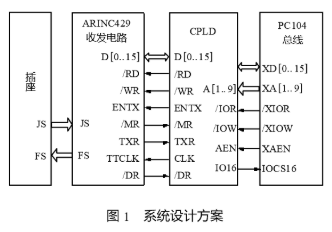

采用可编程器件CPLD实现ARINC429收发电路与接口板的通信设计-PC104总线系统是一种新型的计算机测控平台,作为嵌入式PC的一种,在软件与硬件上与标准的台式PC(PC/AT)体系结构完全兼容,它具有如下优点:体积小、十分紧凑,并采用模块化结构,功耗低,总线易于扩充,紧固堆叠方式安装,适合于制作高密度、小体积、便携式测试设备,因此在军用航空设备上有着广泛的应用,但也正是PC104板的这种小尺寸结构、板上可用空间少给设计带来了一定的困难,所以本设计采用了复杂可编程器件CPLD,用CPLD完成了PC104总线与429总线通讯的主要电路,大大节省了硬件资源,本文着重介绍了CPLD部分的设计。

基于FPGA器件和Libem开发环境实现SpaeeWire Codec接收端的时序设计-SpacewiTe是欧空局2003年提出的一种高速的、点对点、全双工的串行总线网络,面向空间应用。它以IEEE 1355—1995和LVDS标准为基础,提供了一种通用接口标准以简化和规范不同设备之间的互连,对解决目前星上数据处理系统的总线带宽不足有重要作用。而且,随着FPGA容量增大和功耗降低,以及内部软核的广泛应用,使用FPGA开发数字电路,可以缩短设计时间、减少PCB面积、提高系统的可靠性,FPGA已成为解决系统级设计的重要选择方案之一。本文在Actel的集成开发环境Libem下编写了HDL代码,利用内部集成仿真工具Mod—elSim对设计进行了时序仿真。