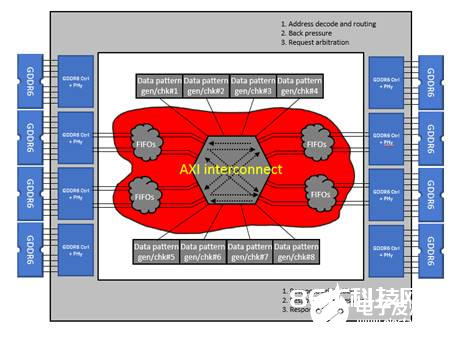

使用2D NoC简化FPGA可编程逻辑功能的应用设计-对于AXI interconnect模块,我们采用Github上开源的AXI4总线连接器来实现,这个AXI4总线连接器将4个AXI4总线主设备连接到8个AXI4总线从设备,源代码可以在参考文献2的链接中下载。我们在这个代码的基础上进行扩展,增加到8个AXI4总线主设备连接到8个AXI4总线从设备,同时加上了跨时钟域逻辑。

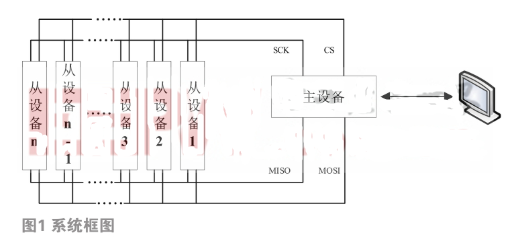

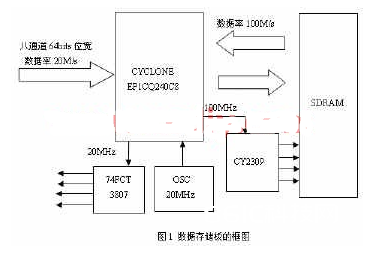

基于可编程逻辑器件实现多路数据采集系统的设计-对于国内而言,正如DSP在20年前出现的情形一样,如今,FPGA正处于数字信号处理技术的前沿。而DSP都是基于一种精简指令集的计算机体系架构,其固定的硬件结构和数据总线宽度已不适合许多面向用户型(可重配置型)的DSP应用系统;其速度也受制于CPU的指令顺序执行的基本工作模式,这已成为DSP处理器一个难以突破的瓶颈。

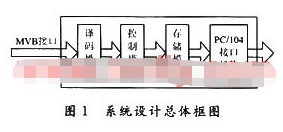

采用可编辑逻辑器件实现MVB总线分析结构的设计-随着高速铁路的迅速发展以及机车车辆的现代化发展趋势,对列车总线的可靠性、安全性、通讯实时性的要求进一步提高,国内的传统的现场总线难于满足要求,而多功能车辆总线(MVB)是快速的过程控制总线,能提供最佳的响应速度,且适合用作车辆总线,这就使得MVB逐渐成为下一代车辆的通信总线标准。随着MVB通信网络应用的日益广泛,我国铁道部已将其作为列车通信的标准平台,国内铁路轨道交通设备制造企业也相继从国外引进装备有MVB网络的列车微机控制系统,一些部门也开展了MVB相关产品的国产化研究和自主研发工作。为了确保不同设备制造厂家生产设备的兼容性,也为了验证所研发的MVB产品的协议一致性,必须对各个MVB设备进行协议一致性测试,以提高MVB设备互连的成功率。在MVB的设计和实施过程中,正确地分析出MVB总线运行状态是一个

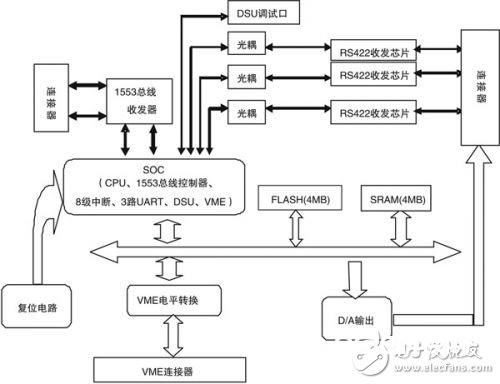

采用EP1C20芯片和S698IP核实现平台计算机的设计-平台计算机采用FPGA+S698IP核的方案(简称SOC),以欧比特公司的S698IP核做为主CPU,另外再把1553B总线控制器、VME总线控制器、3个带FIFO的UART整合在一起。体现了欧比特公司S698IP核灵活、优越性能。并且支持多操作系统。采用SOC设计节省昂贵的流片费用、增加系统设计的灵活性、方便修改、大大缩短设计开发的周期。

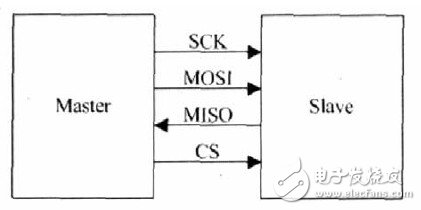

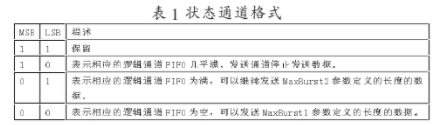

基于可编程逻辑器件实现SPI4.2接口的功能设计-SPI-4.2(System Packet Interface)是 OIF(Optical Internetworking Forum)定义的局部高速总线标准,用于 PHY层芯片到链路层芯片的 10Gbps信号传输。主要应用有 OC-192 ATM、Packet over SONET/SDH(POS)、10Gbps以太网等。

利用CPLD器件和微处理器实现I2C总线控制器的应用方案-I2C总线是PHILIPS公司推出的新一代串行总线,由于其结构简单、灵活,各结点具有独立的电气特性,可实现电路的模块化、标准化而被广泛应用。目前许多MCU都带有I2C总线接口,对没有I2C总线的MCU,可采用软件模拟,有通用软件包可以使用,但功能比较简单。在MCU(以Motorola 68000系列为例)和CPLD电子系统设计中,利用CPLD器件资源,按照I2C总线协议标准模式,设计了功能完善的I2C总线控制器,给出了设计思路和实现方法。

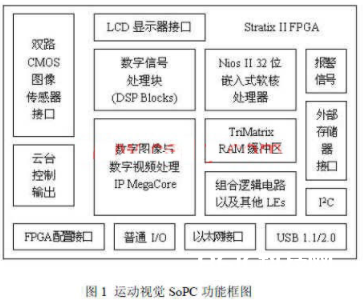

采用StratixII系列FPGA器件实现运动视觉处理系统的设计-该模块主要负责视频图像的采集,摄像头参数的设置和云台步进电机的控制。其中,通过 I2C总线可以设定摄像头内部控制寄存器。在 FPGA中,实现 I2C总线控制器的途径有两种:一种是在 Nios II中用软件模拟实现;另一种是采用第三方,比如 Sciworx,CAST,Digital Core Design等公司提供的 IP核。