就 SystemC 和 SystemVerilog 这两种语言而言, SystemC 是C++在硬件支持方面的扩展,而 SystemVerilog 则继承了 Verilog,并对 Verilog 在面

根据离散小波变换原理的特点,提出了一种基于DWT域的数字水印算法,并用FPGA硬件实现其中关键部分的DWT变换。详细介绍了相关模块的设计和时序,并对整个系统进行了综合仿真,验证了设计的正确性。分析与仿

给出了DPLL的基本概念,阐述了DPLL的缺点,并结合最新的模拟锁相和数字锁相技术,提出了一种基于FPGA的全新锁相倍频系统的设计方法,简单地介绍了设计的思路、原理及其算法,并对该方案的性能进行了分析

介绍一种采用单片SRAM和FPGA实现红外图像显示的新方案,并对显示系统结构、FPGA各功能模块设计、SRAM的读/写时序设计进行了详细论述。该图像显示方案可用于红外图像处理系统的硬件调试和红外图像处

采用VHDL硬件描述语言,以Xilinx公司的FPGA为设计平台,设计实现了以开源软核MC8051为核心的控制单元,控制4路SSI协议模块的SoPC架构的通信控制器,并对通信控制器进行了功能仿真与验证

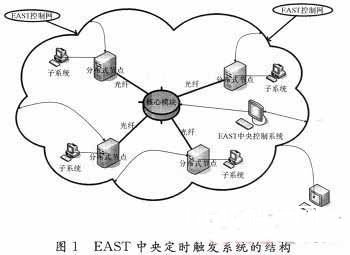

在EAST分布式中央定时同步系统中,时钟分频和触发延迟电路是分布式节点的核心。为了完成对基准时钟信号进行多路任意整数倍的等占空比的分频,并对输入的触发脉冲进行多路任意时间的延迟输出,本设计中采用VHD

介绍了一种基于FPGA的水声信号数据采集与存储系统的设计与实现,给出了系统的总体方案,并对各部分硬件和软件的设计进行了详细描述。系统以FPGA作为数据的控制处理核心,以存储容量达2 GB的大容量NAN

介绍了一种基于FPGA的水声信号数据采集与存储系统的设计与实现,给出了系统的总体方案,并对各部分硬件和软件的设计进行了详细描述。系统以FPGA作为数据的控制处理核心,以存储容量达2GB的大容量NAND