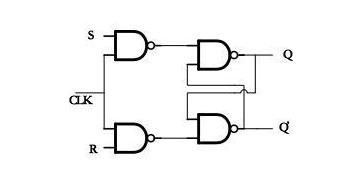

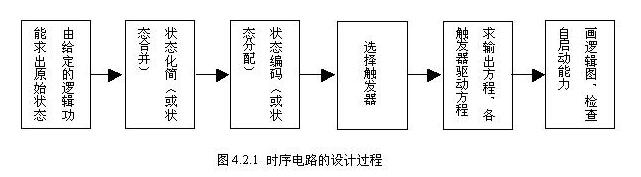

时序逻辑电路设计-数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

数字逻辑电路具有哪些主要特点-从整体上来看,数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。在逻辑功能方面,组合逻辑电路在任一时刻的输出信号仅与当时的输入信号有关,与信号作用前电路原来所处的状态无关;而时序逻辑电路在任一时刻的输出信号不仅与当时的输入信号有关,而且还与电路原来的状态有关。

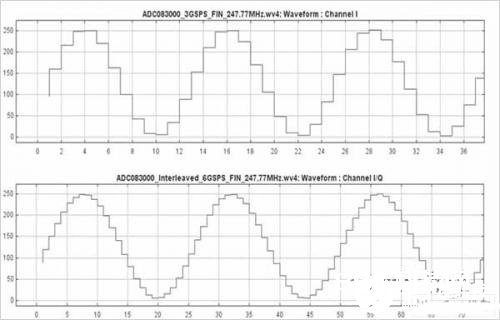

时序交错式类比数位转换器的技术应用和系统设计解决方案-运用时序交错式类比数位转换器(timeinterleavedADC)在每秒高达数十亿次的同步取样类比讯号是一个技术上的挑战,除此之外,对於混合讯号电路的设计也需要非常谨慎小心。基本上,时序交错的目标是利用转换器数目与取样频率相乘而不影响解析度以及动态的效能。

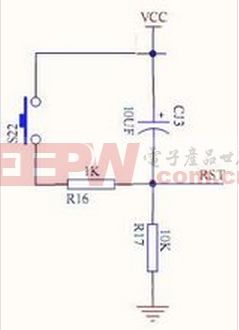

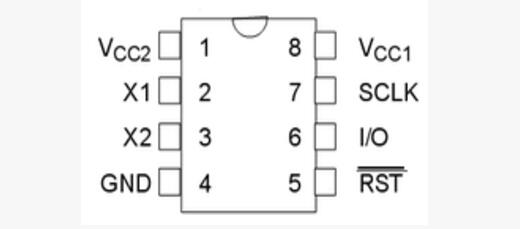

Arduino控制DS1302时钟芯片(ds1302引脚图及功能和应用电路)-本文开始介绍了ds1302引脚图及功能与DS1302封装,其次介绍了两款DS1302应用电路与时序说明,最后介绍了Arduino控制DS1302连线方式及程序说明。

基于SRAM的FPGA的问世标志着现代可重构技术的开端-由于数字逻辑系统功能复杂化的需求,单片系统的芯片正朝着超大规模、高密度的方向发展。对于一个大规模的数字系统而言,系统规模是基于各种逻辑功能模块的组合。但是,无论是时序逻辑系统,还是组合逻辑系统,或者组合/时序混合系统,从时间轴上来看,系统中的各个功能模块并不是时刻都在工作,而是根据系统外部的整体要求,轮流或循环地被激活或工作。并且,随着数字逻辑规模的扩大,在相同速度条件下,在一定的时间区间,其功能模块的平均使用率将下降。因此,系统设计应该从传统追求大规模、高密度的方向,转向如何提高资源利用率,用有限的资源实现更大规模的逻辑设计上来。可重构计算技术能够提供硬件的效率和软件的可编程性,它综合了微处理器和ASIC的特点,在空间维和时间维上均可变。