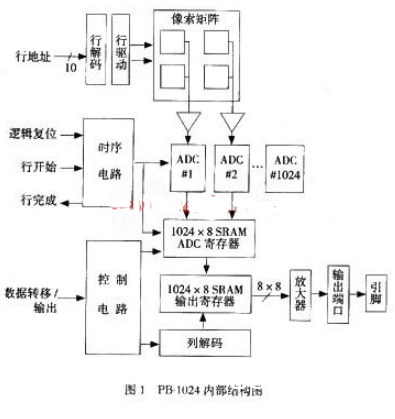

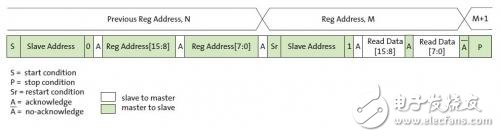

AP0100CS处理器之读写时序详解- AP0100CS集成了具有高级转换器功能的NTSC/PAL编码器,可以提供模拟CCTV市场所需的高TV线分辨率。 这款产品为中国市场设计人员提供了过去无法获取全新相机设计方案。

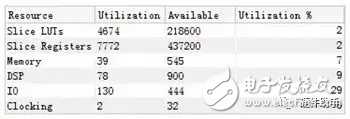

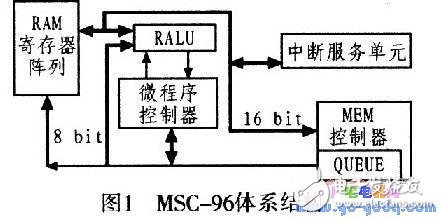

如何设计一个16位的嵌入式微控制器?-使用的FPGA器件是StratixⅡ型号为EP1S40F780C7。综合结果显示:A8096使用3 565个LE(LogIC Element)。时序分析结果:A8096可以运行在49.93 MHz的时钟频率下。A8096占用FPGA资源分布情况如图6所示。

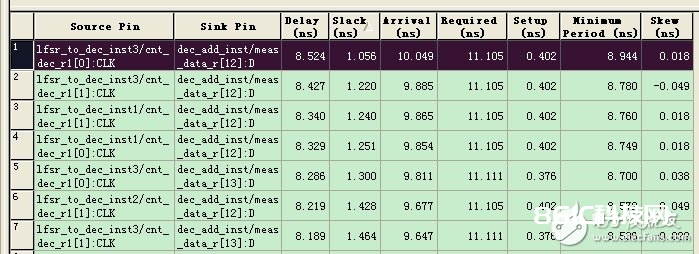

FPGA进行静态时序分析-静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。

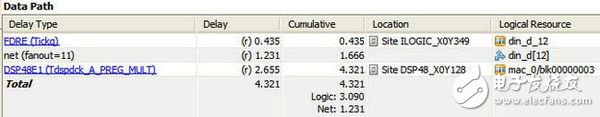

Xilinx的三种高扇出解决方法-Fanout,即扇出,指模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。但是,在某些特殊情况下,受到整体结构设计的需要或者无法修改代码的限制,则需要通过其它优化手段解决高扇出带来的问题。

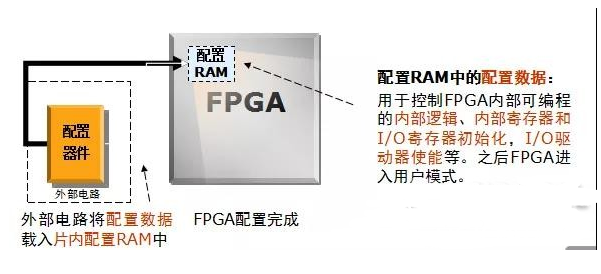

FPGA配置模式选择 FPGA上电加载时序介绍-常见的配置芯片有EPCS 芯片 (EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),还有通用的串行 SPI FLASH 芯片如 M25P40、 M25P16、 W25Q16 等。

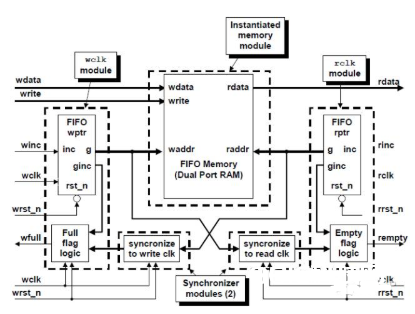

基于各类二进制代码实现异步FIFO的设计-一、概述 在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序要求变得宽松,也提高了它们之间的传输效率。此文内容就是阐述异步FIFO的设计。 二、设计原理 2.1结构框图 Fig. 2.1.1 如上图所示的同步模块synchronize to write clk,其作用是把读时钟域的读指针rd_ptr采集到写时钟(wr_clk)域,然

基于FPGA器件和Libem开发环境实现SpaeeWire Codec接收端的时序设计-SpacewiTe是欧空局2003年提出的一种高速的、点对点、全双工的串行总线网络,面向空间应用。它以IEEE 1355—1995和LVDS标准为基础,提供了一种通用接口标准以简化和规范不同设备之间的互连,对解决目前星上数据处理系统的总线带宽不足有重要作用。而且,随着FPGA容量增大和功耗降低,以及内部软核的广泛应用,使用FPGA开发数字电路,可以缩短设计时间、减少PCB面积、提高系统的可靠性,FPGA已成为解决系统级设计的重要选择方案之一。本文在Actel的集成开发环境Libem下编写了HDL代码,利用内部集成仿真工具Mod—elSim对设计进行了时序仿真。