解读LPC210X之外部中断寄存器-LPC2101/02/03最多包含了三个外部中断输入作为可选择的管脚功能。管脚进行组合后,外部事件可以处理成三个独立的中断信号。外部中断输入能够可选择的用于将处理器从低功耗模式下唤醒。

怎样用STM32单片机的GPIO控制LED显示状态-ODR寄存器可读可写:既能控制管脚为高电平,也能控制管脚为低电平。

管脚对于位写1 gpio 管脚为高电平,写 0 为低电平

BSRR 只写寄存器:[color=Red]既能控制管脚为高电平,也能控制管脚为低电平。

对寄存器高 16bit 写1 对应管脚为低电平,对寄存器低16bit写1对应管脚为高电平。写 0 ,无动作

BRR 只写寄存器:只能改变管脚状态为低电平,对寄存器 管脚对于位写 1 相应管脚会为低电平。写 0 无动作。

STM32单片机SPI的使用原理解析-GPIO_InitTypeDef GPIO_InitStructure;

//配置SPI2管脚

RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO|RCC_APB2Periph_GPIOB, ENABLE);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13 |GPIO_Pin_14| GPIO_Pin_15;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; //复用推挽输出

GPIO_Init(GPIOB, &GPIO_InitStructure);

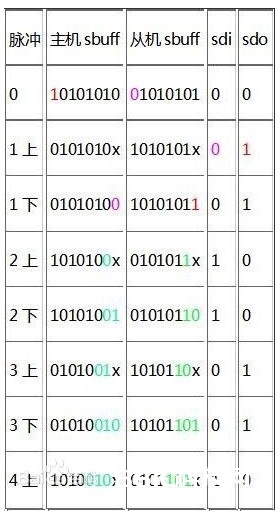

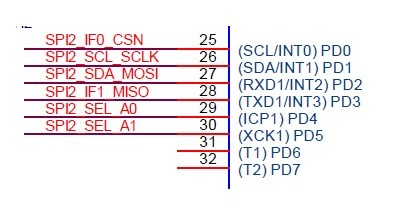

如何解决单片机中的bug模式问题-CSN(IF0)、SCLK(SCL)、RSTN、MOSI(SDA)、MISO(IF1)、AC0(GPIO0)、AC1(GPIO1)(这些管脚中的RSTN、AC0、AC1由FPGA控制),括号内是管脚的第二功能,主要用于芯片复位时的模式设置,具体到SPI模式:在RSTN的上升沿,IF1、IF0要置1,AC0、AC1置0。

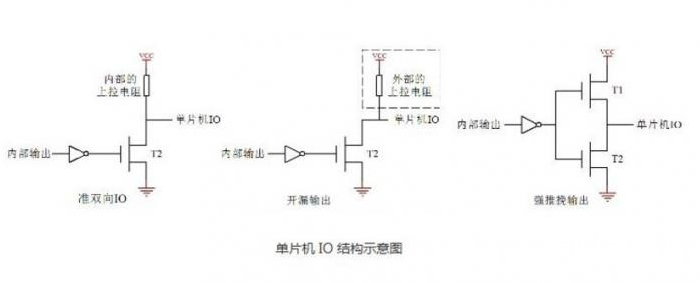

PIC单片机和AVR单片机IO的操作方法解析-51单片机、AVR单片机和PIC单片机IO口结构的均不同,导致了IO口操作也不同。操作单片机IO口的目的是让单片机的管脚输出逻辑电平和读取单片机管脚的逻辑电平。

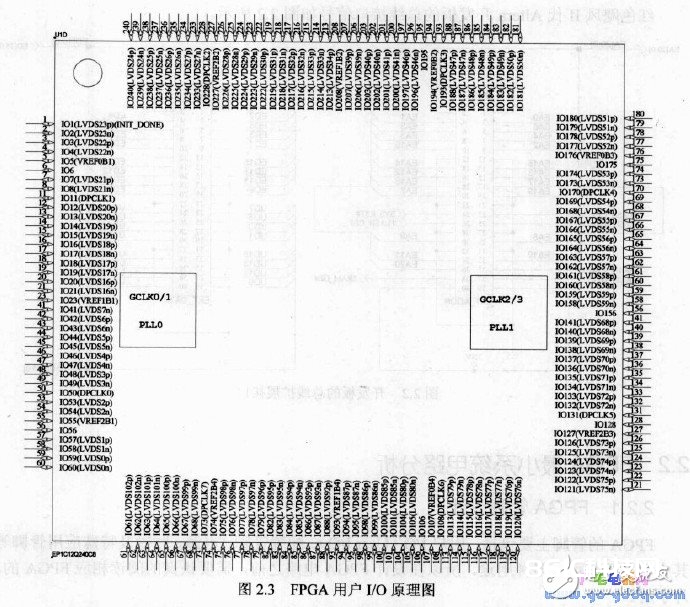

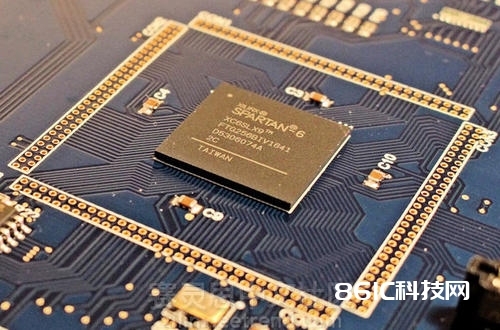

Xilinx 7系列FPGA管脚是如何定义的?-引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到:

FPGA调试过程与特殊管脚-FPGA在上电后,会立刻将nSTATUS配置状态管脚置成低电平,并在上电复位(POR)完成之后释放它,将它置为高电平。作为配置状态输出管脚,在配置过程中如果有任何一个错误发生了,则nSTATUS脚会被置低。

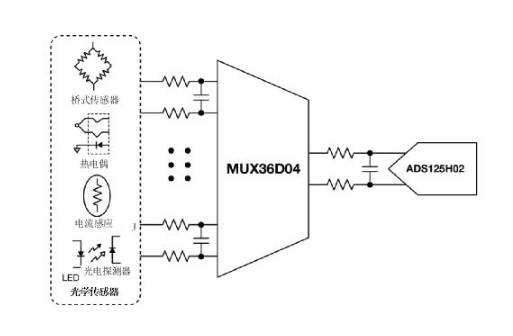

低漏电多路复用器在高阻抗PLC系统中是否重要?-漏电流是一个重要参数,因为它在开关打开和断开时都会导致直流误差。多路复用器数据表有许多与漏电流相关的规格,包括当开关合上或断开时流过源极管脚(IS)或漏极管脚(ID)的漏电流。