跟着ASIC电路结构和功用的日趋杂乱,与其相关的测验问题也日益突出。在芯片测验办法和测验向量生成的研讨进程中,怎么下降芯片的测验本钱现已成为非常重要的问题。DFT(可测性规划)经过在芯片原始规划中刺进各种用于进步芯片可测性的逻辑,然后使芯片变得简单测验,大大下降了芯片的测验本钱。现在比较老练的可测性规划主要有扫描规划、鸿沟扫描规划、BIST(Built In Self Test,内建自测验)等。本文经过对一种操控芯片的测验,证明经过选用刺进扫描链和主动测验向量生成(ATPG)技能,可有效地简化电路的测验,进步芯片的测验覆盖率,大大削减测验向量的数量,缩短测验时刻,然后有效地下降芯片的测验本钱。

依据扫描的DFT办法扫描规划的根本原理

时序电路中时序元件的输出不只由输入信号决议,还与其原始状况有关,因而,对它的毛病检测比组合电路要困难的多。扫描规划便是将时序电路转化为组合电路,然后运用现已很老练的组合电路测验生成体系,来完结测验规划。

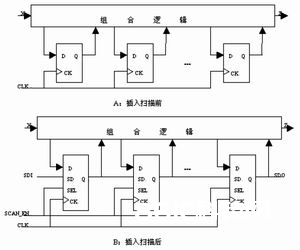

扫描规划可将电路中的时序元件替换为相应的可扫描的时序元件(也叫扫描触发器),然后把它们串起来,构成一个从输入到输出的测验串行移位寄存器(即扫描链),以完成对时序元件和组合逻辑的测验。

如图1所示,选用扫描规划技能后,经过扫描输入端,能够把需求的数据串行地移位到扫描链的相应单元中,以串行地操控各个单元;一起,也能够经过扫描输出端串行地观测它们。这样就消除了时序电路的不行操控性和不行观测性,进步了电路的可测性。需求留意的是,可测性规划的条件是不能改动原始规划的功用。

扫描规划的根本流程

扫描规划测验的完成进程是:

1) 读入电路网表文件,并施行规划规矩查看(DRC),保证规划契合扫描测验的规划规矩;

2) 将电路华夏有的触发器或许锁存器置换为特定类型的扫描触发器或许锁存器(如多路挑选D触发器),而且将这些扫描单元链接成一个或多个扫描链,这一进程称之为测验综合;

3) 测验向量主动生成(ATPG)东西依据刺进的扫描电路以及构成的扫描链主动发生测验向量;

4) 毛病仿真器(Fault Simulator)对这些测验向量施行评价,并确认毛病覆盖率状况。

DFT对芯片的影响

DFT是为了简化芯片测验而选用的技能,对芯片的功用没有影响,但不行避免地会添加逻辑,对芯片发生一些影响。

对芯片面积的影响

DFT以添加逻辑来到达简化测验的意图,添加的逻辑势必会添加芯片面积。一般,选用DFT会添加10%”15%的芯片面积。

对芯片功能的影响

鸿沟扫描要在每个输入输出端口处刺进鸿沟扫描寄存器(BSC),因而,在正常作业时,信号要多经过一个多路开关,这就带来了额定延时,下降了芯片本来能够到达的作业频率。

对芯片毛病覆盖率的影响

芯片测验的要求便是要尽或许地将有毛病的芯片检测出来,然后下降芯片的逃逸率(Escape)。DFT的意图在于便利测验,进步毛病覆盖率,然后下降逃逸率。毛病覆盖率并非越高越好,由于进步毛病覆盖率或许会大大添加测验本钱,所以应该在测验本钱与获得的逃逸率之间进行折衷。