何 进,衣溪琳,张子骥,贺雅娟(电子科技大学 电子科学与工程学院,四川 成都 610054)

摘 要:本文提出一种牢靠的低功耗近似乘法器规划计划,该计划依据嵌入式算法容噪技能,而且经过阈值的合理挑选简化了传统嵌入式容噪计划中的检错纠错模块。咱们依据这样的思路依据SMIC 180 nm工艺规划了相应的8比特乘8比特的近似乘法器。该乘法器在450 MHz的作业频率最低能够作业在1.2 V的电源电压下。与传统的阵列乘法器比较,在相同的作业频率和MSE条件下,传统乘法器能够作业在1.6 V左右,该乘法器能够作业在1.2 V左右,此刻功耗能够下降约40%;与论文[1]中的嵌入式算法容噪乘法器比较,功耗能够下降约16%。

要害词:低功耗;低压;乘法器;算法容噪技能;阈值挑选

0 导言

跟着集成电路的不断发展,芯片的功率密度越来越大,功耗问题成为集成电路规划工程师最关怀的问题之一。在无线传感网络,便携式设备,可植入式医疗设备中,体系对芯片的功耗有严厉的约束 [2,4] 。咱们知道,集成电路的总功耗能够分为动态功耗和静态功耗,动态功耗和静态功耗均与芯片电源电压密切相关,尤其是动态功耗与电源电压的平方成正比。因而,下降芯片的电源电压是下降芯片功耗的最有用的办法 [1] 。可是跟着电源电压的下降,电路的要害途径推迟也会相应增大,此刻有必要下降芯片作业频率,不然要害途径推迟会超越时钟周期,导致芯片功用犯错。可是许多运用场景要求必定的吞吐量,芯片的作业频率会有固定的约束。因而,在作业频率固定的前提下,电源电压的下降被芯片的作业频率约束了。一般在集成电路规划的时分,为了确保电路作业的牢靠性,规划者还需求保存满意的时序裕量来应对制作进程中的工艺差错,噪声搅扰等要素的影响,这些时序的裕量往往是经过电压的裕量来体现的。因而,电路实践能够作业的最小作业电压应该大于理论的临界电压,也便是要害电压 [3] 。

关于数字信号处理的运用来说,不需求芯片得到肯定准确的成果,挨近实在成果的近似值就能满意人类感官的需求。在这些运用傍边,能够经过献身芯片成果的部分精度来下降芯片的功耗和面积。为了进一步下降芯片的作业电压,改善芯片在低压下的牢靠性,Naresh RShanbhag等人提出算法容噪技能 [3] 。该技能针对非准确核算的场景,比方数字信号处理器,神经网络加速器[5][6][7] 等等。该技能与电压缩放技能结合,经过额定的检错和纠错电路补偿因电压过度缩放(VOS)而导致的软过错,使电路的输出的全体成果在低压下到达一个能够接纳的程度。因而,算法容噪技能下降了电路的最小作业电压,下降了电路的功耗而且提升了电路在低压下的稳定性。

可是算法容噪技能有两部分的硬件冗余:一部分是“估量器”,它用来产生一个近似值,是检错纠错的根底;另1部分是“检错纠错模块”。为了处理榜首部分冗余,Sai Zhang等人提出嵌入式算法容噪技能的概念,并解说了怎么经过数据通路分化来把估量器嵌入到主运算电路傍边,然后减小乃至彻底抹去榜首部分冗余 [1] 。

可是第2部分冗余依然没有做任何优化。关于比较大的电路来说,第2部分冗余占的份额比较小,因而不会太重视。可是关于小规模的乘法器,第2部分冗余依然是比较重要的。本文首要是经过优化第2部分硬件冗余来进一步下降嵌入式算法容噪技能的功耗和面积。

本文依据SMIC 180 nm工艺,针对依据嵌入式算法容噪技能的乘法器提出一种合理的优化其检错纠错模块的办法。因为优化了检错纠错模块,使整个电路的面积和功耗有较为显着的下降。

1 算法容噪技能介绍

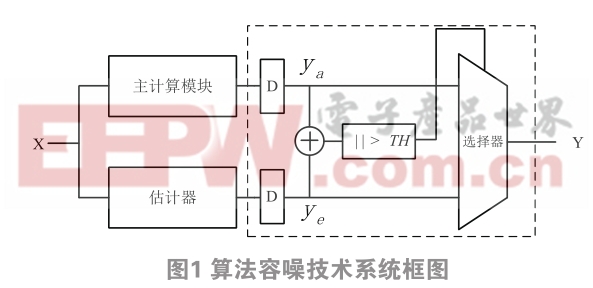

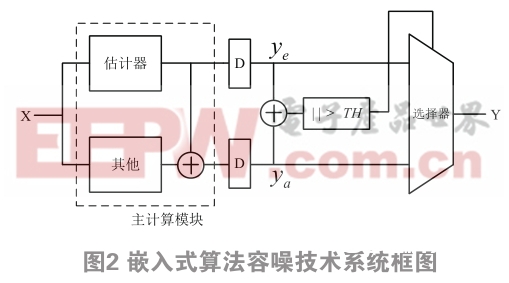

算法容噪技能(ANT)的根本结构如图1所示:包含1个主核算模块,1个估量器,1个检错纠错模块。算法容噪技能需求和电压缩放技能(VOS)结合起来:电压缩放技能下降电源电压,然后下降电路功耗;而算法容噪技能担任补偿因为电压过度缩放而导致的软过错。

其具体作业原理是:当电路的电源电压缩放到要害电压以下时,运算电路就会产生软过错,而且软过错总是优先在成果的高位产生,此刻会导致信号的精度严峻下降。在算法容噪体系中,估量器需求同步输出主核算模块的估量值,而且在电压缩放的范围内,估量器自身应该确保不产生软过错。检错纠错模块经过比较主核算模块的输出和估量器的输出的差值是否大于预设的阈值来判别主核算模块的高位是否呈现了软过错。假如检测到成果的高位呈现了软过错,阐明主核算模块的成果差错很大,此刻就运用估量器的输出作为整个体系终究的输出;不然,就运用主核算模块的输出作为整个电路终究的输出,如公式(1)所示。

经过这样的补偿方法,算法容噪技能终究经过引进一个较小的差错,来确保整个体系的全体输出依然满意近似电路的目标要求。

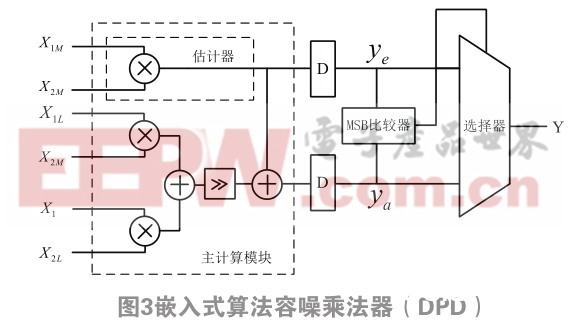

可是,因为加入了估量器和检错纠错模块,算法容噪技能也带来了比较大的额定的硬件开支。嵌入式算法容噪技能把原始的核算进程进行分化成了首要部分和非必须部分两个部分。用来核算首要部分的电路作为估量器,首要部分和非必须部分的和作为主核算模块的成果,这样就完成了把估量器嵌入到了主核算模块,然后处理了估量器带来的硬件开支。

2 检错纠错模块的改善

虽然嵌入式算法容噪技能能够去掉估量器的硬件耗费,可是没有对检错纠错模块中的开支进行优化。因为这部分的硬件开支是比较确认的,即1个加法器,1个取肯定值模块,1个比较器,1个多路复用器等。因而这些硬件开支关于大的规划来说所占份额较小,可是关于小规模的运算模块例如乘法器仍是很重要的。

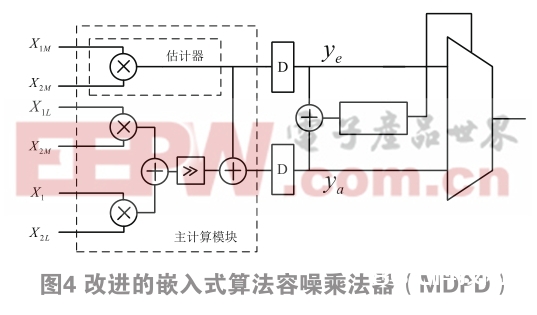

为了进一步简化检错纠错模块,咱们提出了经过阈值的优化挑选来优化这一部分的硬件复杂度。关于一般的阈值,检错纠错模块需求进行相减,取模,比较,才干生成正确的挑选信号。可是咱们发现适量缩放阈值巨细后,只需求简略的持平判别逻辑就能够生成正确的挑选信号。

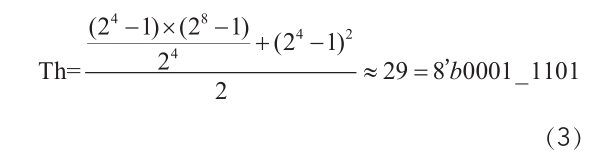

一般的算法容噪技能的阈值由公式(2)确认:

即理论的阈值便是针对恣意的输入,在不产生软过错的情况下,估量器和主核算模块的最大差值。关于如图3所示的8乘8的嵌入式算法容噪技能乘法器来说,它的理论阈值等于主核算模块中除掉估量器的部分的最大值。因而,取,x1=8'b1111_1111,x2=8'b1111_1111此刻得到的差值便是最大差值。依据其完成的进程,能够得到

为了削减检错纠错模块的硬件耗费,咱们能够合理地调理这个阈值。例如,可适当添加或许减小这个阈值,使之变成 2 1n− 。关于上述的8乘8的嵌入式算法容噪乘法器,咱们能够调理阈值为Th=31=8'b0001_1111。这样咱们就能够经过比较主核算模块和估量器的输出的最高几位是否持平来判别主核算模块是否产生软过错。如图4,然后去掉了检错纠错模块所需求的加法器、取模模块、巨细比较器,下降了其硬件复杂度。经过阈值缩放,咱们能够将加法器,肯定值模块,比较器终究用几个同或门来替代,大大下降了检错纠错模块的硬件复杂度。

3 仿真成果比较

3.1 仿真条件和设置

依据前面的思路,咱们规划了一个8乘8的改善型嵌入式算法容噪乘法器(MDPD),而且依据SMIC 180 nm工艺对该乘法器、传统阵列乘法器(DIR)和嵌入式算法容噪乘法器(DPD)进行了相同条件的仿实在验,而且对它们的仿真成果进行了比照。

咱们用同一组随机数据作为乘法器的输入,仿真了三种乘法器结构在各个电压450 MHz的采样频率下的均方差错(MSE)和功耗。为了正确反响电路在不同电压下的实践体现,咱们选用nanosim和VCS对3种乘法器结构进行了晶体管级的混合仿真。

3.2 MSE的比较

均方差错(mean-square error,MSE)是反映估量量与被估量量之间差异程度的一种衡量,能够用来衡量近似电路与的近似作用。假如均方差错小,阐明近似电路的近似作用好。

咱们从1.0 V~1.8 V每距离0.02 V取一个电压进行了仿真,得到了如图5所示的3种乘法器结构的均方差错随电压改变的曲线图。从图上能够看到依据算法容噪技能的乘法器关于软过错有比较好的容错才能,在1.2 V之前其均方差错都没有显着的上升,而一般的阵列乘法器的均方差错随电压下降上升显着。因而,在相同的均方差错下,算法容噪的乘法器MDPD和DPD能够作业在更低的电压,大约能够下降0.4 V。

3.3 功耗比照

对应于试验运用的电源电压,得到了3种结构在不同的电压下的功耗。MDPD和DPD得益于主核算模块的近似完成,因而主核算模块比阵列乘法器DIR硬件开支小。而经过咱们优化往后的MDPD就有比较显着的功耗下降。如图6所示,在1.8 V的电源电压下,MDPD的功耗比DPD小约16%。

4 定论

在这篇文章中,咱们针对算法容噪技能进行了改善,经过阈值挑选优化了嵌入式算法容噪技能乘法器的检错纠错模块。在保存了嵌入式算法容噪技能的根本功用和功能的一起,改善的嵌入式算法容噪乘法器在450MHz的作业频率下最低能够作业到1.2 V,比较一般的阵列乘法器最低作业电压能够下降0.4 V,比较改善前的嵌入式算法容噪乘法器,功耗能够下降约16%。

参考文献

[1] Zhang S, Shanbhag N R.Embedded Algorithmic Noise-Tolerance for Signal Processing and Machine Learning Systems viaData Path Decomposition. IEEE Transactions on Signal Processing, 2016,64(13): 3338-3350.

[2] Abdallah R A, Shanbhag N R. An Energy-Efficient ECG Processor in 45-nm CMOS Using Statistical Error Compensation. IEEEJournal of Solid-State Circuits, 2013,48(11): 2882-2893.

[3] Shim B, Sridhara S R,Shanbhag N R. Reliable low-power digital signal processing via reduced precision redundancy. IEEETransactions on Very Large Scale Integration (VLSI) Systems, 2004,12(5):497-510.

[4] Wey I, Peng C C, Liao F Y. Reliable Low-Power Multiplier Design Using Fixed-Width Replica Redundancy Block[J]. IEEETransactions on Very Large Scale Integration Systems, 2015, 23(1):78-87.

[5] Lin Y, Zhang S, Shanbhag N R. Variation-Tolerant Architectures for Convolutional Neural Networks in the Near ThresholdVoltage Regime[C]. IEEE International Workshop on Signal Processing Systems. IEEE, 2016.

[6] Zhang S, Shanbhag N R. Embedded error compensation for energy efficient DSP systems.2014:30-34.

[7] Zhang S, Shanbhag N R. Reduced overhead error compensation for energy efficient machine learning kernels. 2015:15-21.

作者简介:

何进 (1993-),男,硕士研讨生,首要研讨方向:低功耗数字集成电路规划。

贺雅娟 (1978-),女,副教授,首要研讨方向:专用集成电路与体系、超低压超低功耗数字集成电路规划等。

本文来源于科技期刊《电子产品世界》2019年第8期第46页,欢迎您写论文时引证,并注明出处