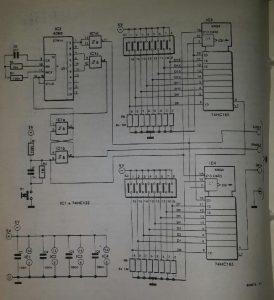

数据生成器提供了一种简单的电路测试方法,无需复杂的软件。所有必要的组件都很容易接近。该电路设计围绕 SDA3002 型电路的时序进行构建,采用三线连接而不是两线 I2C 格式。在仅需要单个固定数据字的情况下,可以省略 DIP 开关 S2 和 S3 以及八倍拉电阻阵列。这导致 IC3 和 IC4 的输入保持在固定电平。该发生器的基础是两个级联移位寄存器(IC3 和 IC4),用作与串行转换器并行运行的 16 位寄存器。

串行数据发生器示意图

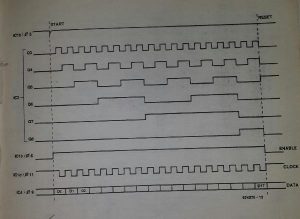

整个测试周期的开始由启动信号标记。参见图2的时序图,IC2的输出23经过IC1d反相,作为移位寄存器的时钟源。这种安排可确保 D0 在整个时钟周期内保持在输出状态,持续 1.25 ms。当达到高输出 18 次时,双稳态复位,IC1 的输出 23(与 IC2 的输出 25 和 28 连接)将启用线拉低,结束周期。

在此图中,总共 18 位经历了移位。两个最高有效位 (MSB) 受 IC3 串行输入的影响。如果该输入寄存器为高电平,则 D16 和 D17 被设置为“1”。如果需要灵活地使这些位成为变量,则必须引入一个或两个作为移位寄存器连接的附加双稳态。当所有位都为高电平时,发生器的电流消耗(主要由下拉电阻决定)仍然非常低,约为 80。按下 S1 后,振荡器会短暂激活,使电流加倍。

串行数据发生器示意图