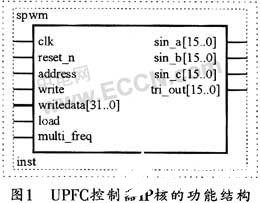

使用Altera CycloneIIEP2C35评估板实现UPFC控制器IP核的设计-UPFC控制器的IP主要用来输出3路相位分别相差2π/3的正弦波形数据和3路相位分别相差2π/3的三角载波波形数据。由于UPFC控制系统采用SPWM调制技术,所以要求UPFC控制器IP输出的正弦波频率应跟电网频率保持一致,输出的正弦波幅值和相位可以根据需要进行调节;而输出的三角载波频率、幅值和相位则保持不变。

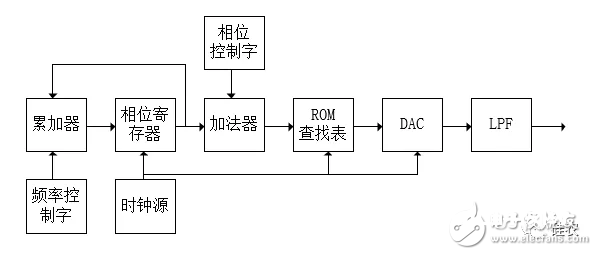

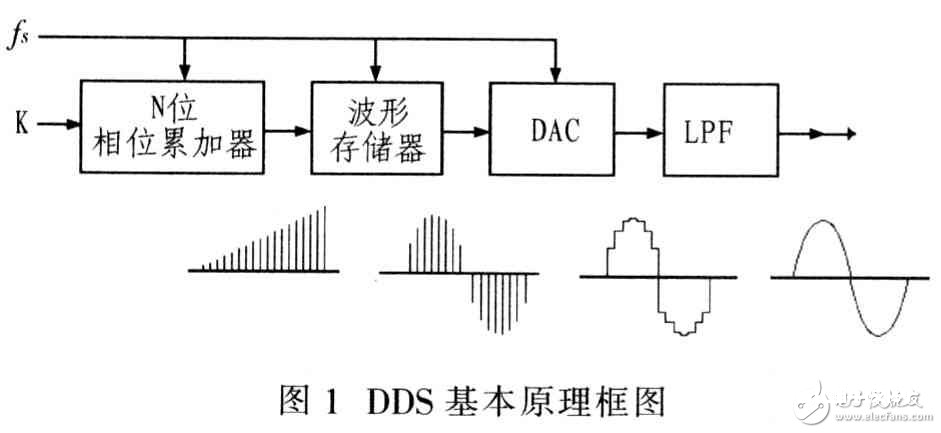

采用FPGA实现DDS任意波形发生器设计-在系统时钟脉冲的作用下,相位累加器不停累加,即不停查表,把波形数据送到D/A转换器转换成模拟量输出,从而合成波形。滤波器则进一步平滑D/A转换器输出的近似正弦波的锯齿阶梯波,同时衰减不必要的杂散信号。

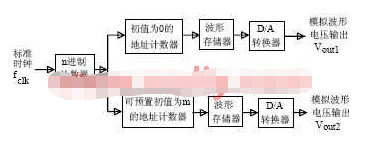

基于FPGA器件和VHDL语言实现波形及移相波形发生器的系统设计-标准时钟(由晶振电路产生)加于进制可编程的n进制计数器,其溢出脉冲加于可预置初值的地址计数器,生成波形存储器所需的地址信号,地址信号的产生频率正比于时钟频率,且周而复始地变化,从而使波形数据存储器输出周期的正弦序列,D/A转换器则输出连续的模拟正弦电压(或电流)波形,如图2所示。

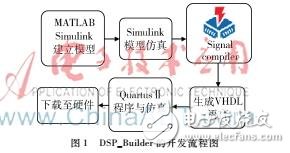

基于FPGA的可调FIR滤波器在实际通信系统中的实现方法设计- 基于灵活自适应的空口波形技术FOFDM(Filtered OFDM)是现代通信技术的研究热点,设计并实现可调FIR滤波器是实现该技术的核心工作之一。本文设计的基于FPGA的可调节FIR滤波器系数的自适应调整是通过控制算法对信道中的信号进行快速检测,然后将结果和滤波器的输出结果进行差值计算进行反馈调节。利用Quartus II和DSP Builder设计基于FPGA的16阶系数可调FIR滤波器,给出核心模块的设计电路图和仿真结果。仿真结果表明:基于灵活自适应空口波形技术可以在FPGA上实现,而且由于FPGA具有天然的并行性,实际的通信系统中可以采用并发模式进行,达到提高信号传送速率的目的。

UPFC控制器IP核的主要功能及设计方案分析-统一潮流控制器(Unified Power Flow Con-troller,简称UPFC)是一种可以较大范围地控制电流使之按指定路经流动的设备,它可在保证输电线输送容量接近热稳定极限的同时又不至于过负荷。控制系统是UPFC的核心部分,它的主要功能是监测交流电网的传输和控制输出逆变波形,不但能使输出波形的频率跟定电网频率,而且可对输出波形的幅值和相位进行调节。

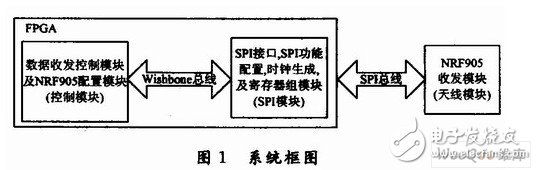

以FPGA控制为核心的NRF905无线通信系统设计-系统建立起来后,下一步是最终的板级验证。图6为用Chipscope得到的波形图。mosi与miso分别是发送端与接收端SPI总线上的信号。从图中可以看出数据基本吻合,由此表明设计的以FPGA控制NRF905的无线通信系统能够正常工作。

失物报警器设计电路-CMOS反相电路IC1a、1b组成RC振荡器产生2kHz调制波,其输出经IC1c缓冲、D1整流后加到Tr1的基极形成偏置电压。调制波形从变成“H”到振荡开始的时间约268ns。调制波的频率不能超过3.7MHz。